ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 16.10.2024

Просмотров: 3

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Липецкий государственный технический университет

Факультет автоматизации и информатики

Кафедра автоматизированных систем управления

Индивидуальное домашнее задание

по дисциплине Архитектура вычислительных систем

«Разработка вычислительной системы на основе определенного процессора»

| Студент Группа ПИ-20-2 | | Арнаутов М. С. |

| Руководитель | | Болдырихин О. В. |

Липецк 2022 г.

Задание кафедры

Изучить материал по теме: техническую документацию по выбранному

процессору, периодическую, учебную и другую литературу.

Выбрать необходимые дополнительные элементы для данного процессора для реализации вычислительной системы.

Создать схему вычислительной системы в программе Proteus.

Разработать управляющую программу для данной вычислительной системы.

Запустить, протестировать и отладить систему, исследовать ее работу.

Управление электродвигателем постоянного тока с помощью микроконтроллера ATmega 32.

Ход работы

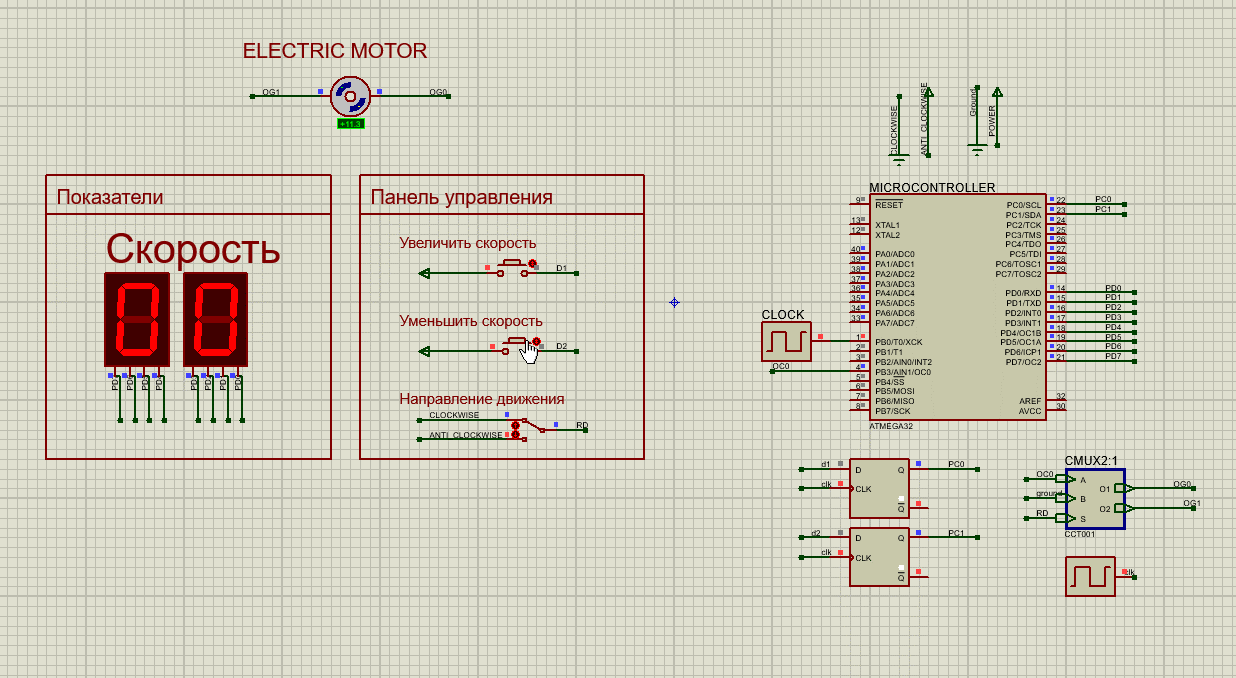

Схема созданной системы представлена на рисунке 1.

Рисунок 1 – Разработанная система

Спецификация элементов схемы представлена в таблице 1.

Таблица 1 – Спецификация схемы

| № | Обозначение | Элемент | Количество |

| 1 | MC | ATmega32 микроконтроллер | 1 |

| 2 | DTFF | Триггер (flip-flop) D-типа с прямым и инверсным выходами. | 2 |

| 3 | SSeg | Семисегментный двоично-десятичный индикатор | 2 |

| 4 | CLOCK | Генератор тактовых импульсов | 2 |

| 5 | ELECTRIC MOTOR | Электродвигатель постоянного тока | 1 |

Описание элементов:

ATmega32 микроконтроллер

AVR – представляет собой 8-разрядный микроконтроллер общего назначения c RISC-ядром.

Кристаллы AVR имеют «на борту» Flash-память программ, память данных EEPROM и SRAM, порты ввода-вывода и типовые для 8-битных микроконтроллеров периферийные устройства. Некоторые серии кристаллов содержат блок LCD, интерфейсы CAN и USB.

Гарвардская архитектура AVR в сочетании с одноуровневым конвейером обеспечивает производительность 1MIPS на 1МГц. В отличие от «классической» архитектуры 8051, платформа AVR содержит регистровый файл из 32 регистров общего назначения, что существенно повышает скорость пересылки данных при работе программы.

AVR-архитектура, на основе которой построены микроконтроллеры семейства, объединяет мощный гарвардский RISC-процессор с раздельным доступом к памяти программ и данных, 32 регистра общего назначения, каждый из которых может работать как регистр-аккумулятор, и развитую систему команд фиксированной 16-бит длины. Большинство команд выполняются за один машинный такт с одновременным исполнением текущей и выборкой следующей команды, что обеспечивает производительность до 1 MIPS на каждый МГц тактовой частоты.

32 регистра общего назначения образуют регистровый файл быстрого доступа, где каждый регистр напрямую связан с АЛУ. За один такт из регистрового файла выбираются два операнда, выполняется операция, и результат возвращается в регистровый файл. АЛУ поддерживает арифметические и логические операции с регистрами, между регистром и константой или непосредственно с регистром.

Регистровый файл также доступен как часть памяти данных. 6 из 32-х регистров могут использоваться как три 16-разрядных регистра-указателя для косвенной адресации. Старшие микроконтроллеры семейства AVR имеют в составе АЛУ аппаратный умножитель.

Базовый набор команд AVR содержит 120 инструкций. Инструкции битовых операций включают инструкции установки, очистки и тестирования битов.

Все микроконтроллеры AVR имеют встроенную FLASH ROM с возможностью внутрисхемного программирования через последовательный 4-проводной интерфейс.

Периферия МК AVR включает: таймеры-счётчики, широтно-импульсные модуляторы, поддержку внешних прерываний, аналоговые компараторы, 10-разрядный 8-канальный АЦП, параллельные порты (от 3 до 48 линий ввода и вывода), интерфейсы UART и SPI, сторожевой таймер и устройство сброса по включению питания. Все эти качества превращают AVR-микроконтроллеры в мощный инструмент для построения современных, высокопроизводительных и экономичных контроллеров различного назначения.

В рамках единой базовой архитектуры AVR-микроконтроллеры подразделяются на три подсемейства:

-

Classic AVR — основная линия микроконтроллеров с производительностью отдельных модификаций до 16 MIPS, FLASH ROM программ 2–8 Кбайт, ЕEPROM данных 64–512 байт, SRAM 128–512 байт; -

mega AVR с производительностью 1–16 MIPS для сложных приложений, требующих большого обьёма памяти, FLASH ROM программ 4–128 Кбайт, ЕEPROM данных 64–512 байт, SRAM 2–4 Кбайт, SRAM 4 Кбайт, встроенный 10-разрядный 8-канальный АЦП, аппаратный умножитель 8x8; -

tiny AVR — низкостоимостные микроконтроллеры в 8-выводном исполнении имеют встроенную схему контроля напряжения питания, что позволяет обойтись без внешних супервизорных микросхем.

AVR-микроконтроллеры поддерживают спящий режим и режим микропотребления. В спящем режиме останавливается центральное процессорное ядро, в то время как регистры, таймеры-счётчики, сторожевой таймер и система прерываний продолжают функционировать. В режиме микропотребления сохраняется содержимое всех регистров, останавливается тактовый генератор, запрещаются все функции микроконтроллера, пока не поступит сигнал внешнего прерывания или аппаратного сброса. В зависимости от модели, AVR-микроконтроллеры работают в диапазоне напряжений 2,7–6В либо 4–6В (исключение составляет ATtiny12V с напряжением питания 1,2 В).

Средства отладки. ATMEL предлагает программную среду AVR-studio для отладки программ в режиме симуляции на программном отладчике, а также для работы непосредственно с внутрисхемным эмулятором. AVR-studio доступен с WEB-страницы ATMEL, содержит ассемблер и предназначен для работы с эмуляторами ICEPRO и MegaICE. Ряд компаний предлагают свои версии Си-компиляторов, ассемблеров, линковщиков и загрузчиков для работы с микроконтроллерами семейства AVR. Как и продукция MICROCHIP, микроконтроллеры ATMEL широко применяются в России и, как следствие, программируются многими отечественными программаторами. Ряд российских фирм предлагает также различные аппаратные средства отладки AVR-микроконтроллеров.

Структурная схема AVR микроконтроллера представлена на рисунке 2.

Рисунок 2 – Структурная схема

Блоки на схеме:

-

JTAG Interface (Joint Test Action Group Interface) - интерфейс внутрисхемной отладки (4 провода); -

FLASH - перепрограммируемая память для сохранения программы; -

Serial Peripheral Interface, SPI - последовательный периферийный интерфейс (3 провода); -

EEPROM (Electrically Erasable Programmable Read-Only Memory) - перепрограммируемое ПЗУ, энергонезависимая память; -

CPU (ЦПУ) - центральный процессор управления, сердце микроконтроллера, 8-битное микропроцессорное ядро; -

ALU (АЛУ) - арифметико-логическое устройство, основа блока CPU; -

RAM (Random Access Memory) - оперативная память процессора; -

Program Counter - счетчик команд; -

32 General Purpose Registers - 32 регистра общего назначения; -

Instruction Register - регистр команд, инструкций; -

Instruction Decoder - декодер команд; -

OCD (On-Chip Debugger) - блок внутренней отладки; -

Analog Comparator - аналоговый компаратор, блок сравнения аналоговых сигналов; -

A/D Converter (Analog/Digital converter) - аналогово-цифровой преобразователь; -

LCD Interface (Liquid-Crystal Display Interface) - интерфейс для подключения жидко-кристаллического дисплея, индикатора; -

USART (Universal Asynchronous Receiver-Transmitter), UART - универсальный асинхронный приемопередатчик; -

TWI (Two-Wire serial Interface) - последовательный интерфейс с двухпроводным подключением; -

Watchdog Timer - сторожевой или контрольный таймер; -

I/O Ports - порты вода/вывода; -

Interrupts - блок управления и реакции на прерывания; -

Timers/Counters - модули таймеров и счетчиков.

Микроконтроллеры AVR имеют систему сокращенного набора команд RISC, хотя целиком и не полностью попадают под это определение.

Система RISC подразумевает полную симметрию между ресурсами памяти разного типа. Это, в частности, позволяет обращаться к регистрам, портам и памяти данных одними и теми же командами, что и обуславливает их небольшое количество. Однако, несмотря на то, что адресное пространство памяти AVR действительно непрерывно, всё же три разных его области используются только для своих специфических целей. РОН – преимущественно для математических операций, РВВ – для управления процессором, ОЗУ – только как хранилище информации. В связи с этим существуют группы команд как для работы с каждым видом памяти в отдельности, так и для пересылки данных из одной области памяти в другую. Поэтому и количество команд AVR достаточно велико. В фирменной документации, где много говорится про ортогональность ядра, в первую очередь имеется в виду полная равноправность именно РОН.

Большинство команд ассемблера используют различные ячейки памяти микроконтроллера и, соответственно, содержат кроме кода операции (КОП) также их адреса. В зависимости от того в каком виде в команде хранится адрес различают два способа адресации: прямую и косвенную. В первом случае адрес ячейки задан явно, а во-втором он находится в одном из регистров-указателей (у AVR это 16-разрядные регистры X,Y,Z). У микропроцессоров различного типа, оба способа адресации могут иметь множество вариаций.

Семисегментный двоично-десятичный индикатор

Индикатор представляет собой обычный 7-сегментный индикатор со встроенным дешифратором BCD-7Seg.

7-сегментные цифровые индикаторы – устройства, состоящие из 7 светодиодов, которые установлены в форме цифры 8. С помощью зажигания отдельных сегментов отображаются цифры от 0 до 9, а также некоторые буквы (обычно латинского алфавита).

Триггер (flip-flop) D-типа с прямым и инверсным выходами.

При появлении активного фронта (переход из 0 в 1) на входе CLK, сигнал на входе D фиксируется на выходе Q. Активный фронт можно изменить, применив свойство INVERT=CLK. Асинхронный вход SET (активный уровень 1) устанавливает триггер в состояние 1, а асинхронный вход RESET (активный уровень 1) сбрасывает триггер в состояние 0.

Описание работы и устройства системы.

Для генерации тактового импульса используется внешний генератор. Порт D предназначен для отображения текущей скорости на семисегментных индикаторах. Для изменения скорости имеются две кнопки, которые соединены с триггерами, на выходе которых генерируются сигналы счета вверх или вниз, которые в свою очередь подаются на порт C.

Изменение направления вращения происходит без участия микроконтроллера. Схема элемента CMUX 2:1, отвечающего за направление вращения, представлена на рисунке 3.

Рисунок 3 – Элемент CMUX

Демонстрация работы приведена на рисунках 4-6.

Рисунок 3 – Увеличение скорости вращения

Рисунок 4 – Уменьшение скорости вращения

Рисунок 5 – Изменение направления и увеличение скорости вращения

Вывод

В ходе выполнения индивидуального домашнего задания мной были изучены устройство и система команд микроконтроллера AVR, были получены навыки разработки управляющей программы для микропроцессора архитектуры RISC на языке ассемблер.

Приложение А

Код управляющей программы

.equ TCCR0Config = 0b01100110

.equ PortBDDR = 0b00001000

.equ LoopDelayA = 255

.equ LoopDelayB = 12

.include "m32def.inc"

.org 0

rjmp start

.org $0050

start:

ldi r16, $FF

out ddra, r16

out ddrd, r16

ldi r16, PortBDDR

out ddrb, r16

ldi r16, $FC

out ddrc, r16

ldi r16, 0

out TCNT0, r16

ldi r16, 0

out OCR0, r16

ldi r16, TCCR0Config

out TCCR0, r16

InfLoop:

IncCheck:

SBIS pinc, 0

rjmp DecCheck

in r25, OCR0

cpi r25, 255

brsh DecCheck

inc r25

out ocr0, r25

rjmp delay

DecCheck:

SBIS pinc, 1

rjmp Delay

in r26, OCR0

cpi r26, 1

brlo Delay

dec r26

out ocr0, r26

Delay:

in r17, OCR0

out portd, r17

ldi r18, 0

ldi r19, 0

CounterLoop:

inc r18

cpi r18, LoopDelayA

brsh CounterLoop2

rjmp CounterLoop

CounterLoop2:

ldi r18, 0

inc r19

cpi r19, LoopDelayB

brsh InfLoop

rjmp CounterLoop

rjmp InfLoop