Файл: Отчет по лабораторной работе 3 по дисциплине Цифровая электроника.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 03.02.2024

Просмотров: 7

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра РС

отчет

по лабораторной работе №3

по дисциплине «Цифровая электроника»

Вариант 5

| Студент гр. 1404 | | Сухов Ю.П. |

| Преподаватель | | Богданов Д. В. |

Санкт-Петербург

2023

-

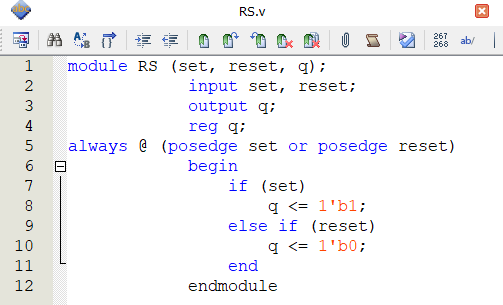

Собрать схему асинхронного RS-триггера в текстовом редакторе. Для этого воспользоваться кодом из приложения.

Рис. 1 – код для RS-триггера

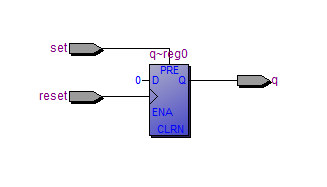

Изучить схему, реализованную в RTL-Viewer.

Рис. 2 – схема в RTL-Viewer

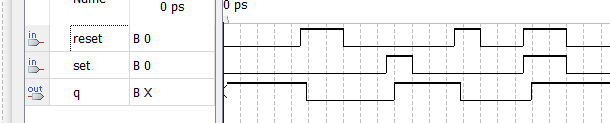

Построить временные диаграммы, иллюстрирующие работу устройства

Рис. 3 – временная диаграмма с задержкой RS-триннера

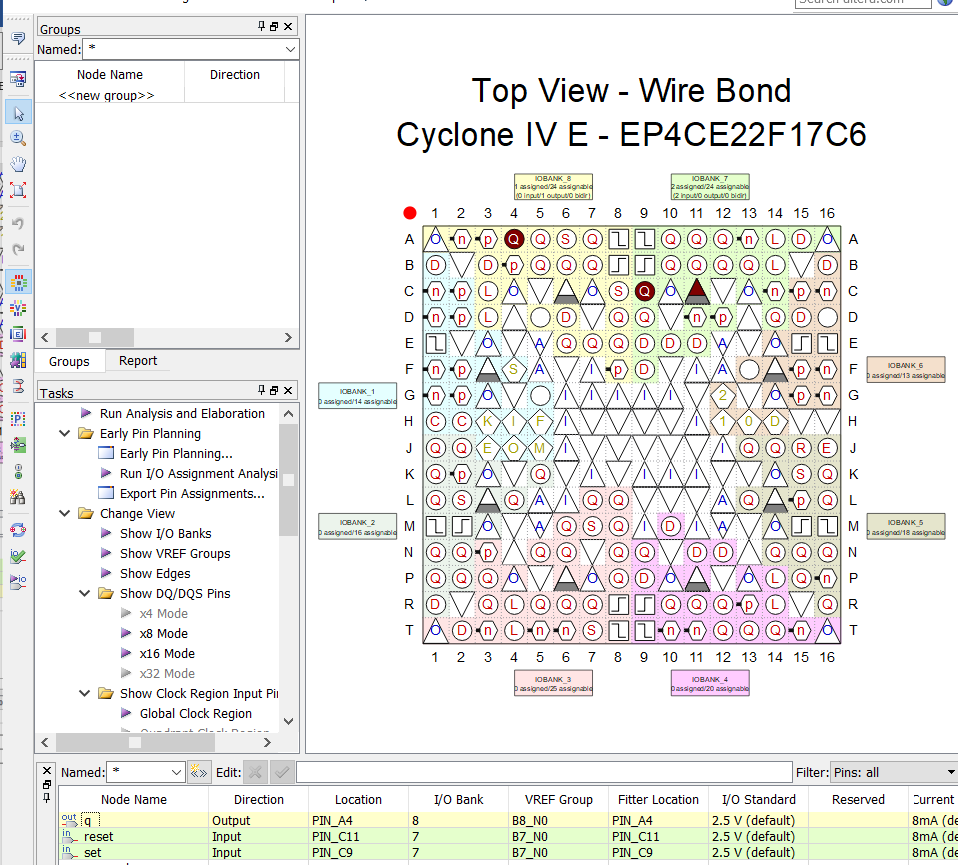

Запрограммировать в отладочную плату. Тип ПЛИС – Altera Cyclone IV E EP4CE22F17C6. Указать входные сигналы на SW1(set), SW5(reset), выходной – на LED3.

Рис. 4 – PinPlanner RS-триггера

-

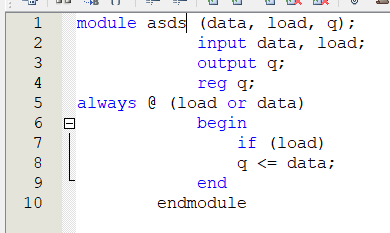

Собрать схему асинхронного DL-триггера в текстовом редакторе. Для этого воспользоваться кодом из приложения.

Рис. 5 – код для DL-триггера

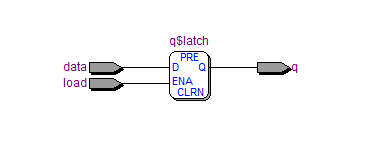

Изучить схему, реализованную в RTL-Viewer.

Рис. 6 – схема в RTL-Viewer

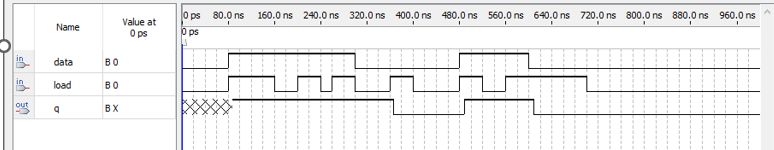

Построить временные диаграммы, иллюстрирующие работу устройства

Рис. 7 – временная с задержкой диаграмма DL-триггера

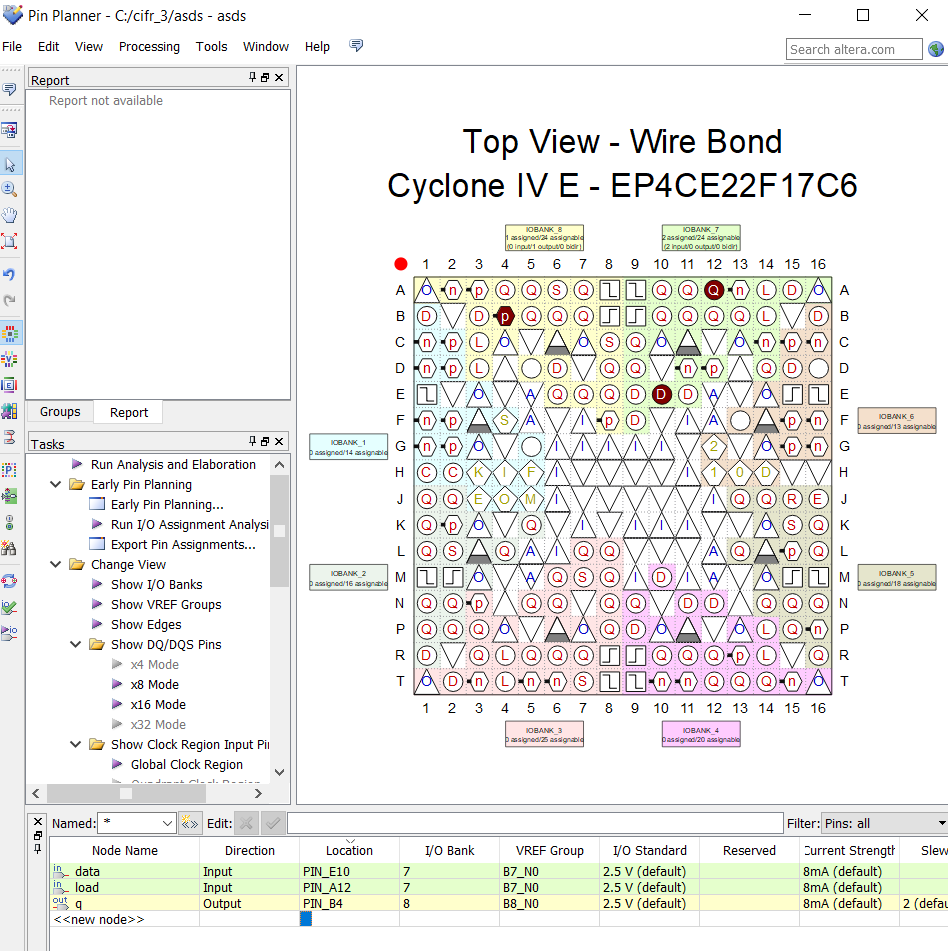

Запрограммировать в отладочную плату. Тип ПЛИС – Altera Cyclone IV E EP4CE22F17C6. Указать входные сигналы на SW4(data), SW7(load), выходной – на LED4.

Рис. 8 – PinPlanner DL-триггера

Вывод: в ходе данной лабораторной работы были изучены RS и DL триггеры, построены временные диаграммы с задержкой и зашит в плату код для каждого триггера.

RS-триггер сбрасывает значение если вход reset принимает значение 1 и возвращает входное значение если единице равняется set.

DL-триггер сохраняет значение data, если load равен единице, и не даёт его изменить если load равен нулю.