Файл: Литература по курсу аос (по всем вопросам должен быть представлен краткий рукописный конспект в общей тетради).docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 08.02.2024

Просмотров: 94

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Создается процесс.

Деление ВАП процесса на страницы аналогично страничной организации памяти:

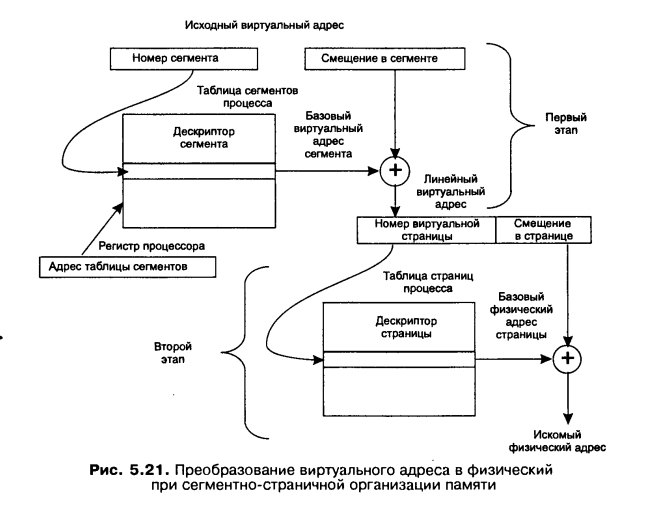

Итак, преобразование виртуального адреса в физический:

Ура!!!

Механизм сегментации и страничный механизм здесь довольно изолированы друг от друга, и могут быть независимо изменены.

Например, страничный механизм может быть многоуровневый (добавились разделы, описанные в страничной реализации). Так, например, работают некоторые процессоры Интел, в т.ч Интел Пентиум.

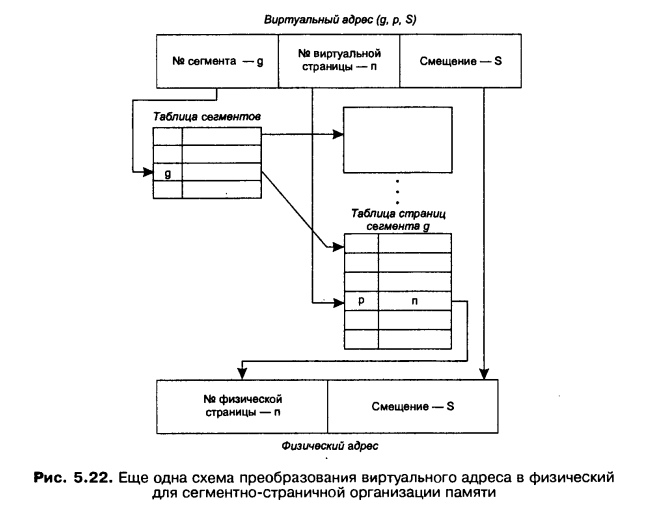

Сегментно-страничное управление памятью можно реализовать по-другому:

Преобразование адреса в такой схеме еще красивше:

Ура!!!

Организация виртуальной памяти, преобразование адреса.

Перечитай все, что касается виртуальной памяти и тд и пересказывай.

Обмен данными между процессами на основе виртуальной памяти.

Основная задача ОС по управлению памятью – защита областей памяти, принадлежащих разным потокам, от несанкционированного вмешательства.

Однако иногда нужно наоборот, организовать контролируемый совместный доступ нескольких потоков к одному участку памяти.

Сегмент памяти в этом случае называется РАЗДЕЛЯЕМОЙ ПАМЯТЬЮ.

При работе с виртуальной памятью это сделать можно по-разному:

Функции работы ОС по работе с разделяемой памятью:

ОС может создавать разделяемый ресурс:

Выгрузка разделяемых сегментов на диск ничем не отличается от выгрузки индивидуальных сегментов.

Небольшое вступление про процессоры IA-32 и аппаратную поддержку мультипрограммирования

Аппаратные средства поддержки мультипрограммирования есть во всех современних процессорах, в полной мере есть они и в семействе 32-разрядных процессоров Intel: Pentium, Pentium Pro, Pentium 2, 3, Celeron, 80386, 80486. Архитектуру этих процессоров называют еще IA-32 или х86.

Процессоры х86 могут работать в:

- реальном режиме (разработан для совместимости с процем 8086, 16-разрядные инструкции и 1 Мб оперативы)

- защищенном режиме (основной режим работы проца);

Важную роль в организации вычислительного процесса играют регистры процессора, поэтому эту страшную мутотень надо подробно рассмотреть. Одно утешение – на ТСИСе тоже это надо сдавать на экзамене. Так что бьем двух зайцев.

Группы регистров процессоров Пентиум:

Есть 8 32-разрядных РОН.

К первым 4 регистрам можно обращаться:

6 регистров – ссылаются на дескрипторы сегментов памяти:

Все они, кроме первого, доступны программно (туда можно загрузить новое значение с помощью команды);

Каждый сегмент хранит в себе СЕЛЕКТОР – 16-разрядное число.

Структура селектора:

EIP + CS(из регистров сегментов) = виртуальный адрес инструкции.

- флаг знака

- флаг нуля

- флаг переполнения

- флаг паритета

- флаг переноса и тд

- флаг разрешения аппаратных прерываний (разрешение аппаратных прерываний IF)

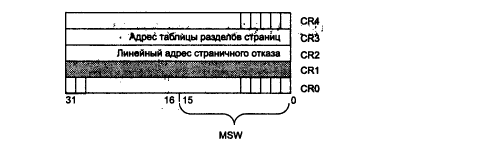

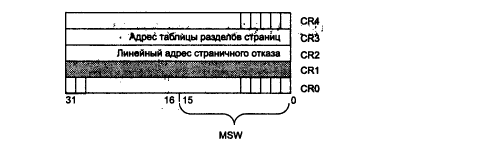

5 управляющих регистров: CR0, CR1, CR2, CR3, CR4 – хранят данные об общем состоянии процессора.

CR0 – все основные признаки:

- реальный / защищенный режим

- вкл / выкл страничного механизма

- признаки, влияющие на работу кэша и выполнение команд с плавающей точкой

CR1 – зарезервирован

CR2 – линейный адрес страничного отказа

CR3 – физический адрес таблицы разделов

CR4 – работа архитектурных расширений (возможность использования страниц > 4 Мб)

Адреса важных системных таблиц и структур, связанных с управлением процессами и памятью.

+ В этих регистрах хранятся лимиты, ограничивающие размер этих таблиц.

Регистры отладки – значения точек останова

Регистры тестирования – проверка корректности работы внутренних блоков процессора.

Средства поддержки сегментной организации памяти в процессорах Пентиум

(собственно ответ на билет)

Процессор Пентиум – 32 разрядный, поэтому максимальный размер физической ОП, на которую он может отображать ВАП – 4 гига.

Процессор Пентиум может поддерживать как сегментную, так и сегментно-страничную организацию памяти.

-

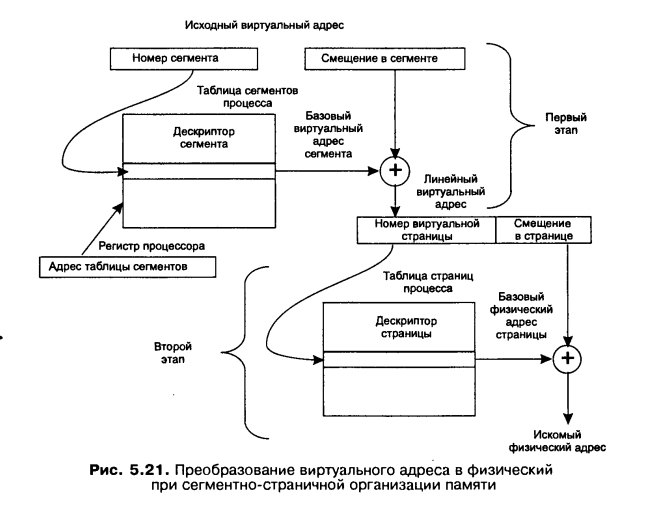

ОС создает для процесса таблицу сегментов, где содержатся дескрипторы всех сегментов (все, как при сегментной организации, только базовый адрес указывается НЕ ФИЗИЧЕСКИЙ, а начальный линейный виртуальный адрес сегмента) -

ОС, используя начальный линейный виртуальный адрес сегмента, преобразовывает пару (номер сегмента + смещение в сегменте) в ЛИНЕЙНЫЙ ВИРТУАЛЬНЫЙ адрес байта. -

Потом, используя СТРАНИЧНЫЕ механизмы, этот линейный виртуальный адрес байта преобразуется в физический.

Деление ВАП процесса на страницы аналогично страничной организации памяти:

-

Размер страницы – степень двойки -

Нумерация виртуальных страниц – в пределах ВАП процесса -

Нумерация физических страниц – в пределах оперативной памяти. -

Для каждого процесса также ведется ТАБЛИЦА СТРАНИЦ -

В память загружаются / выгружается только часть страниц процесса по разным всяким механизмам. -

Базовый адрес таблицы страниц и таблицы сегментов – часть контекста процесса, они хранятся в специальных регистрах процессора.

Итак, преобразование виртуального адреса в физический:

-

Механизм сегментации (добываем линейный виртуальный адрес):

-

Дано: номер сегмента, смещение -

В спец регистре хранится базовый адрес таблицы сегментов -

Базовый адрес + номер сегмента = адрес дескриптора сегмента -

Анализ полей дескриптора (разрешен ли доступ к сегменту) -

Из дескриптора добываем базовый адрес сегмента + смещение = линейный виртуальный адрес.

-

Страничный механизм (получаем физический адрес)

-

Линейный виртуальный адрес раскладывается на номер страницы и смещение внутри страницы (отделение энного к-ва младших бит, в зависимости от размера страницы) -

В спец регистре хранится адрес таблицы страниц, оттуда добываем дескриптор нужной страницы, и находим соответствующий номер физической страницы -

К номеру физической страницы прибавляем смещение = физический адрес.

Ура!!!

Механизм сегментации и страничный механизм здесь довольно изолированы друг от друга, и могут быть независимо изменены.

Например, страничный механизм может быть многоуровневый (добавились разделы, описанные в страничной реализации). Так, например, работают некоторые процессоры Интел, в т.ч Интел Пентиум.

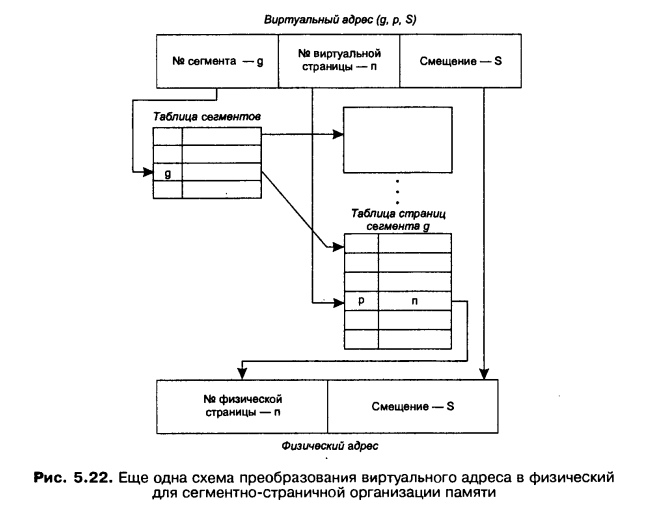

Сегментно-страничное управление памятью можно реализовать по-другому:

-

ВАП процесса делим на сегменты -

Сегменты делим на виртуальные страницы, но они нумеруются В ПРЕДЕЛАХ СЕГМЕНТА, а не всего ВАП процесса. -

Виртуальный адрес задается 3 параметрами: Номер Сегмента + Номер Страницы + Смещение в Странице. -

У каждого процесса – своя таблица сегментов, хранится в регистре. -

У каждого СЕГМЕНТА – своя таблица страниц -

В таблице страниц – дескрипторы страниц, без особенностей -

В таблице сегментов – дескрипторы сегментов хранят АДРЕС ТАБЛИЦ СТРАНИЦ.

Преобразование адреса в такой схеме еще красивше:

-

Есть номер сегмента, находим адрес соответствующей таблицы страниц -

Есть номер страницы, находим номер физической страницы -

К нему конкатенируем смещение.

Ура!!!

Организация виртуальной памяти, преобразование адреса.

Перечитай все, что касается виртуальной памяти и тд и пересказывай.

Обмен данными между процессами на основе виртуальной памяти.

Основная задача ОС по управлению памятью – защита областей памяти, принадлежащих разным потокам, от несанкционированного вмешательства.

Однако иногда нужно наоборот, организовать контролируемый совместный доступ нескольких потоков к одному участку памяти.

-

Например, несколько пользователей работают с одной программой. Данные у них должны быть, конечно, в двух экземплярах, но код программы – в одной. -

Или для межпроцессного обмена данными, когда один поток пишет данные в буфер, а второй – оттуда читает.

Сегмент памяти в этом случае называется РАЗДЕЛЯЕМОЙ ПАМЯТЬЮ.

При работе с виртуальной памятью это сделать можно по-разному:

-

Поместить разделяемый виртуальный сегмент в общую часть ВАП, где модули ОС располагаются. Тогда настройка дескриптора сегмента производится только один раз, все процессы ею пользуются. -

Поместить разделяемый сегмент в ВАП каждого процесса, и настроить параметры отображения этих виртуальных сегментов на одну область оперативной памяти.

-

При сегментной организации для этого надо – в дескрипторах виртуального сегмента указать один и тот же базовый физический адрес -

При сегментно-страничной – надо настроить таблицу страниц каждого процесса -

При чисто страничной – не выйдет, нет понятия сегмент.

Функции работы ОС по работе с разделяемой памятью:

-

Поддержка схемы именования ресурсов -

Проверка прав доступа процесса к ресурсу -

Отслеживать, сколько процессов пользуются ресурсом

ОС может создавать разделяемый ресурс:

-

По запросу (через системный вызов – все процессы, запрашивающие создание разделяемого ресурса с одним и тем же id, могут им пользоваться) -

По умолчанию – например, когда поступает несколько запросов на выполнение одного и того же приложения.

Выгрузка разделяемых сегментов на диск ничем не отличается от выгрузки индивидуальных сегментов.

-

Аппаратная поддержка сегментной организации памяти в системах на основе процессоров с архитектурой IA32.

Небольшое вступление про процессоры IA-32 и аппаратную поддержку мультипрограммирования

Аппаратные средства поддержки мультипрограммирования есть во всех современних процессорах, в полной мере есть они и в семействе 32-разрядных процессоров Intel: Pentium, Pentium Pro, Pentium 2, 3, Celeron, 80386, 80486. Архитектуру этих процессоров называют еще IA-32 или х86.

Процессоры х86 могут работать в:

- реальном режиме (разработан для совместимости с процем 8086, 16-разрядные инструкции и 1 Мб оперативы)

- защищенном режиме (основной режим работы проца);

Важную роль в организации вычислительного процесса играют регистры процессора, поэтому эту страшную мутотень надо подробно рассмотреть. Одно утешение – на ТСИСе тоже это надо сдавать на экзамене. Так что бьем двух зайцев.

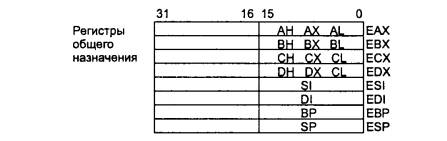

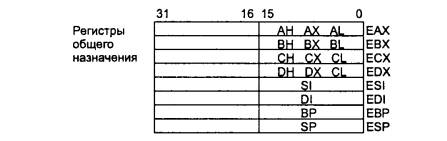

Группы регистров процессоров Пентиум:

-

РОН – регистры общего назначения -

Регистры сегментов -

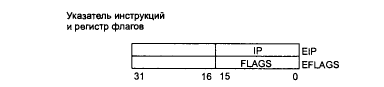

Указатель инструкций -

Регистр флагов -

Управляющие регистры -

Регистры системных адресов -

Регистры отладки и тестирования + регистры математического сопроцессора (для выполнения операций с плавающей точкой);

-

РОН

Есть 8 32-разрядных РОН.

-

Первые 4 РОН: А, B, C, D – для хранения операндов команд (арифметических, логических и всяких прочих) -

Последние 4 – ESI, EDI, EBP, ESP – для задания смещения внутри сегмента данных. Используются совместно с регистрами сегментов (см дальше) для задания виртуального адреса.

К первым 4 регистрам можно обращаться:

-

Целиком (EAX, EBX, ECX, EDX) -

К младшему их байту (AL, BL, CL, DL); -

Ко второму по старшинству байту (AH, BH, CH, DH); -

К двум младшим байтам (AX, BX, CX, DX);

-

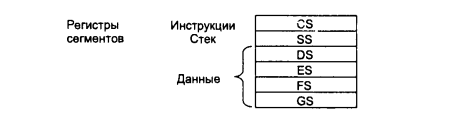

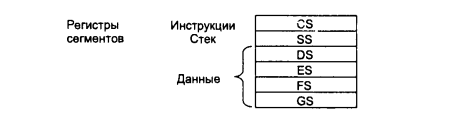

Регистры сегментов

6 регистров – ссылаются на дескрипторы сегментов памяти:

-

CS – дескриптор кодового сегмента -

SS – дескриптор сегмента стека -

DS, ES, FS, GS – дескрипторы сегментов данных

Все они, кроме первого, доступны программно (туда можно загрузить новое значение с помощью команды);

Каждый сегмент хранит в себе СЕЛЕКТОР – 16-разрядное число.

Структура селектора:

| 12 разрядов | 1 разряд | 3 разряда |

| Индекс в таблице дескрипторов сегментов | Показывает, где находится дескриптор: - в GDT - в LDT | Поле RPL – уровень привилегий запроса к этому сегменту |

-

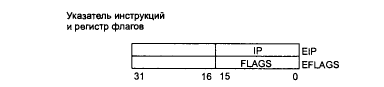

Указатель инструкций EIP – содержит смещение адреса текущей инструкции.

EIP + CS(из регистров сегментов) = виртуальный адрес инструкции.

-

Регистр флагов (EFLAGS) – содержит признаки, характеризующие результат выполнения операции:

- флаг знака

- флаг нуля

- флаг переполнения

- флаг паритета

- флаг переноса и тд

- флаг разрешения аппаратных прерываний (разрешение аппаратных прерываний IF)

-

Управляющие регистры:

5 управляющих регистров: CR0, CR1, CR2, CR3, CR4 – хранят данные об общем состоянии процессора.

CR0 – все основные признаки:

- реальный / защищенный режим

- вкл / выкл страничного механизма

- признаки, влияющие на работу кэша и выполнение команд с плавающей точкой

CR1 – зарезервирован

CR2 – линейный адрес страничного отказа

CR3 – физический адрес таблицы разделов

CR4 – работа архитектурных расширений (возможность использования страниц > 4 Мб)

-

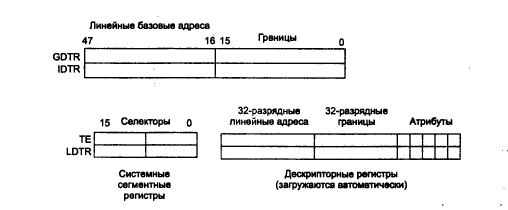

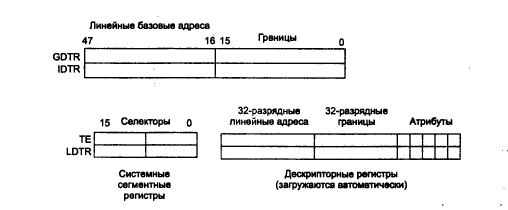

Регистры системных адресов

Адреса важных системных таблиц и структур, связанных с управлением процессами и памятью.

-

GDTR – Global Descriptor Table Register – физический 32-разрядный адрес глобальной таблицы дескрипторов (GDT) – общая часть ВАП для всех процессов -

IDTR – Interrupt Descriptor Table Register – физический 32-разрядный адрес таблицы дескрипторов прерываний (IDT) – она используется для вызова процедур обработки прерываний.

+ В этих регистрах хранятся лимиты, ограничивающие размер этих таблиц.

-

TR – task register – индекс дескриптора сегмента состояния задачи TSS (он в DTR лежит) -

LDTR – Local Descriptor Table Register – индекс дескриптора сегмента локальной таблицы дескриптора LDT (индивидуальная часть ВАП процесса);

-

Регистры отладки и тестирования

Регистры отладки – значения точек останова

Регистры тестирования – проверка корректности работы внутренних блоков процессора.

Средства поддержки сегментной организации памяти в процессорах Пентиум

(собственно ответ на билет)

Процессор Пентиум – 32 разрядный, поэтому максимальный размер физической ОП, на которую он может отображать ВАП – 4 гига.

Процессор Пентиум может поддерживать как сегментную, так и сегментно-страничную организацию памяти.

-

Сегментные средства работают всегда (верхний уровень); -

Страничные средства могут быть вкл/выкл (это нижний уровень);