Файл: Мультипроцессоры(ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ).pdf

Добавлен: 14.03.2024

Просмотров: 75

Скачиваний: 0

СОДЕРЖАНИЕ

ГЛАВА 1. ВЫБОР АППАРАТНО-ПРОГРАММНЫХ И ПРОГРАММНЫХ СРЕДСТВ ДЛЯ РАЗРАБОТКИ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ

1.1 ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

1.2. СРЕДСТВО АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ QUARTUSII

1.3. СРЕДА СИСТЕМНОЙ ИНТЕГРАЦИИ QSYS

1.4. ВСТРАИВАЕМЫЙ ПРОЦЕССОР NIOS II

1.5 ВСТРАИВАЕМЫЙ ПРОЦЕССОР MICROBLAZE

1.6. СРЕДСТВО РАЗРАБОТКИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ NIOS II SBT FOR ECLIPSE

ГЛАВА 2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ

2.1. ПРЕИМУЩЕСТВА ИЕРАРХИЧЕСКИХ МНОГОПРОЦЕССОРНЫХ СИСТЕМ

2.2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ NIOS II

2.3. КОНСТРУКЦИИ АППАРАТНЫХ СРЕДСТВ ДЛЯ СОВМЕСТНОГО ИСПОЛЬЗОВАНИЯ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.3.2. АВТОНОМНЫЕ МУЛЬТИПРОЦЕССОРЫ

2.3.3. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ С ОБЩЕЙ ПЕРИФЕРИЕЙ

2.4. ИСПОЛЬЗОВАНИЕ ОБЩИХ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ

2.4.1. РАЗДЕЛЯЕМЫЕ ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА

2.4.2. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПАМЯТИ

2.4.3. ЯДРО АППАРАТНОГО МЬЮТЕКСА

2.4.4. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.5. ПЕРЕКРЫТИЕ АДРЕСНОГО ПРОСТРАНСТВА

2.6. ПРОЕКТИРОВАНИЕ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ДЛЯ НЕСКОЛЬКИХ ПРОЦЕССОРОВ

2.6.1. ПРОГРАММИРОВАНИЕ ПАМЯТИ

В многопроцессорных системах необходимость подключения различных компонентов очень зависит от реализации разработки. Поэтому при проектировании многопроцессорных систем необходимо убедиться, что каждый компонент подключен к желаемому процессору. Наиболее лучше компоненты управляются одним процессором. Если процессор A требует доступ к периферийному устройству, которое подключено к процессору Б и управляется им, процессор A должен запросить у процессора B, чтобы он выполнял операции с периферийным устройством от имени процессора A. Для этой цели мы можем использовать общую память, защищенную мьютексом для связи между двумя процессорами.

2.5. ПЕРЕКРЫТИЕ АДРЕСНОГО ПРОСТРАНСТВА

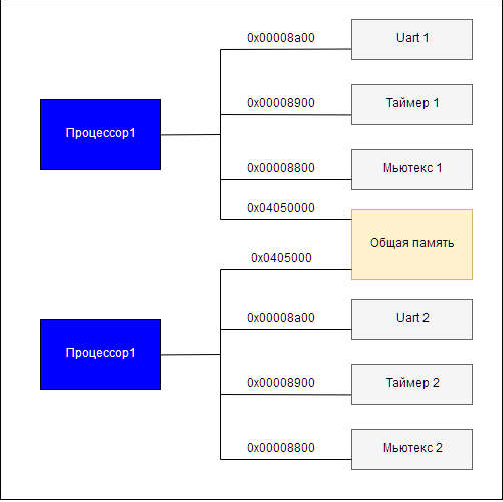

Однопроцессорные системы обычно не допускают более одного ведомого периферийного устройства, занимающего одно и то же адресное пространство, поскольку такая организация вызывает конфликты. Однако в многопроцессорных системах отдельные ведомые периферийные устройства могут занимать один и тот же базовый адрес без конфликта, поскольку каждое периферийное устройство управляется другим процессором. Поскольку не каждое периферийное исключительно устройство ведомого обязательно обрабатывается каждым процессором, каждый процессор может иметь другое представление о системе. Если процессор А подключен к ведомому периферийному устройству, записанному по адресу 0x8a00, процессор Б может подключается к отдельному ведомому периферийному устройству, которое записано по тому же адресу, до тех пор, пока процессор А не подключен к периферийному устройству процессора Б, а процессор Б – не подключен к периферийному устройству процессора А. В сущности, двухточечное соединение позволяет двум процессорам иметь отдельные адресные пространства. На рисунке 8 показан блок диаграммы примерной многопроцессорной системы с различными подчиненными компонентами с одним базовым адресом.

Рис. 8. Многопроцессорная ведомая периферия, с одним базовым адресом

2.6. ПРОЕКТИРОВАНИЕ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ДЛЯ НЕСКОЛЬКИХ ПРОЦЕССОРОВ

2.6.1. ПРОГРАММИРОВАНИЕ ПАМЯТИ

При создании многопроцессорной системы мы можем запустить про- граммное обеспечение для несколько процессоров из одного физического запоминающего устройства. Программное обеспечение для каждого про- цессора должно располагаться в своем собственном уникальном регионе памяти, но эти регионы могут находиться в том же физическом запоми- нающем устройстве. Для программного обеспечения каждого процессора требуется 8 килобайт (КБ) памяти для кода программы и для данных. Пер- вый процессор может использовать область между 0x0 и 0x1FFF памяти на кристалле в качестве своего программного пространства, а второй процес- сор может использовать область между 0x2000 и 0x3FFF.

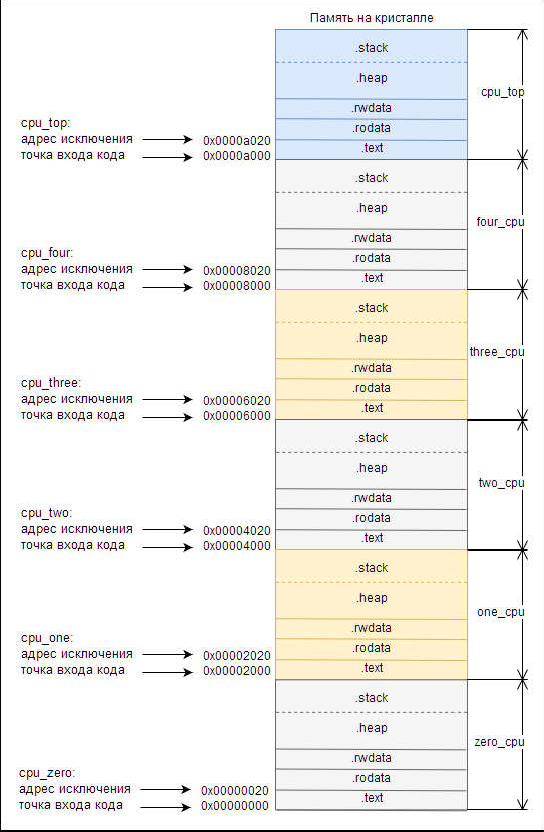

Nios II SBT предоставляет собой простую схему разбиения памяти, которая позволяет использовать несколько процессоров для запуска своего программного обеспечения из разных регионов одной и той же физической памяти. SBT использует адрес исключения для каждого процессора при определении области памяти, из которой каждый процессор может выпол- нить свой код. Разработчик системы устанавливает адрес для каждого про- цессора не зависимо от Qsys. [10][12]

Nios II SBT гарантирует связь программного обеспечения процессора и его места в памяти. Он использует адреса исключений, чтобы вычислить, где находится каждая секция кода. Nios II SBT позиционирует область ко- да каждого процессора в памяти, содержащего адрес исключения.

Если программное обеспечение для нескольких процессоров связано с одной физической памятью, то Nios II SBT использует адрес исключения каждого процессора для определения базового адреса региона. Область кода заканчивается на адресе исключения для следующего процессора определённого в той же памяти. Процессору с наивысшим адресом исключения присваивается область кода, которая продолжается до конца всего адресного диапазона памяти.

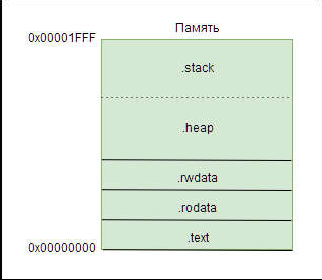

Каждый процессор имеет пять разделов компоновщика по умолчанию. Независимо от того, принадлежит ли процессор однопроцессорной или многопроцессорной системе, секции компоновщика по умолчанию имеют следующий вид:

.text - исполняемый код;

.rodata - любые данные только для чтения, используемые при выполнении кода;

.rwdata - раздел где хранятся переменные значения чтения, записи и указатели;

.heap - раздел где расположена динамически распределенная память;

.stack - раздел параметров функции-вызова и других временных данных.

Эти разделы должны быть связаны и расположены по фиксированным адресам в памяти. На рисунке 9 приведён структурный вид этих секций.

Рис. 9. Секции компоновщика одного процессора.

Рис. 9. Секции компоновщика одного процессора

В многопроцессорной системе может быть полезно использовать единую память для хранения всех секций кода каждого процессора. В этом случае адрес исключения для каждого процессора в Qsys определяет границы между тем, где заканчивается кодовая секция одного процессора и начинается секция кода следующего процессора. [10][13]

Например, можно представить систему, в которой внутренняя память занимает следующие специфические для процессора диапазоны адресов: 0x00050000 to 0x0005FFFF—cpu_top процессор;

0x04000000 to 0x0405FFFF—Nios II процессор в любой подсистеме.

Процессору cpu_top и процессорам в каждой подсистеме выделено 8 КБ встроенной памяти каждому для запуска своего программного обеспе- чения. Если мы используем Qsys для установки их адресов исключений на 8КБ памяти, то Nios II SBT автоматически разбивает память на кристалле на основе этих адресов исключений.

На рисунке 10 приведён пример разделение памяти для системы построенной в данной работе.

Рис.10. Разбиение встроенной памяти для шести процессоров

На этом рисунке показана карта адресов смещений во встроенной памяти определенной в верхнем уровне иерархии. Встроенная память рассматривается процессорами в каждой подсистеме в другом адресном месте.

Этот адрес получается путем добавления базового адреса встроенной памяти, который определен в верхнем уровне, к базовому адресу шины Avalon-MM pipeline bridge, используемой подсистемами для доступа к компонентам верхнего уровня.

В младших шести битах адреса исключения всегда устанавливается 0x20. Смещение 0x0 – это адрес где процессор Nios II должен запустить свой код сброса, поэтому адрес исключения должен быть помещен в другом месте. Смещение 0x20 используется, потому что оно соответствует одной строке кэша команд. 0x20 байтов кода сброса инициализируют кеш команд, а затем разветвляются по адресам исключения для системного кода этого процессора.

Необходимо соблюдать осторожность при разбиении физической памяти на разделы кода нескольких процессоров. В Qsys или Nios II SBT нет гарантий, что мы предоставили достаточно места для кода, стека и кучи разделов каждого процессора. Если в памяти выделяется неадекватное пространство кода, стека или разделов то это может вызвать переполнение и повреждение исполняемого кода процессора.

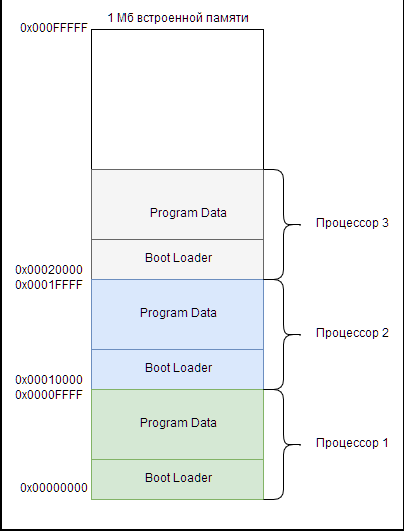

2.6.2 АДРЕСА ЗАГРУЗКИ

В многопроцессорных системах каждый процессор должен загружаться из своего собственного региона памяти. Несколько процессоров не могут успешно загружаться из одного и того же бита исполняемого кода, находящегося в том же адресном пространстве одной энергонезависимой памяти. Загрузочная память может быть разделена также, как и программная память, но понятия разделов и ссылок не вызывают беспокойства, поскольку код загрузки обычно просто копирует реальный программный код туда, где он определён в ОЗУ, а затем его исполняет. Для загрузки нескольких процессоров из отдельных регионов на одной энергонезависимой памяти, необходимо просто установите каждый адрес сброса процессора в то место, откуда мы должны загрузить этот процессор. Нужно убедиться, что мы оставили достаточно места между адресами загрузки, для хранения полезной нагрузки. На рисунке 11 приведён пример разделения памяти для загрузки трёх процессоров.

Рис. 11. Разделение памяти для загрузки трех процессоров

Прошивальщик флэш-памяти для Nios II может загрузить загрузочный код для не скольких процессоров в одно устройство флэш-памяти. Он просматривает адрес сброса каждого процессора и использует этот адрес сброса для вычисления смещения во флэш-памяти, где зашит код. Необходим проявлять осторожность при подключении нескольких процессоров Nios II к одному CFI (Common Flash Interface - Общий интерфейс памяти). Поскольку в драйвере CFI нет механизма защиты от одновременного доступа к ней нескольких процессоров - операция чтения может возвращать испорченные данные. [11][14]

В частности, если процессор попытается прочесть с устройства флэш-памяти CFI, которое находится в режиме записи, то данная операция будет работать неправильно. Если другой процессор выдает запрос к устройству флэш-памяти непосредственно перед чтением первого процессора, то память будет находиться в режиме чтения команд во время обработки запроса, а операция чтения не сможет правильно считать данные. По этой причине Altera рекомендует назначить один процессор Nios II в качестве флэш-мастера, который может работать с устройством флэш-памяти и на чтение, и на запись, в любой многопроцессорной системе с общим устройством флэш-памяти. Назначенный процессор может считывать данные с устройства флэш-памяти для других процессоров.

2.6.3 ОТЛАДКА МНОГОПРОЦЕССОРНЫХ ПРОЕКТОВ NIOS II

Nios II SBT for Eclipse включает в себя ряд функций, которые могут помочь в разработке программного обеспечения для многопроцессорных систем. Наиболее примечательной является способность Nios II SBT for Eclipse для одновременной отладки нескольких процессоров. [12][15] Несколько сеансов отладки могут выполняться одновременно в многопроцессорной системе и могут быть приостановлены и возобновлены для каждого процессора независимо. Точки остановы также могут быть установлены индивидуально для каждого процессора. Если один процессор попадает в точку остановы, он не останавливается и не влияет на работу других процессоров. Сеансы отладки можно запускать и останавливать независимо.

ЗАКЛЮЧЕНИЕ

По результатам данной курсовой работы можно сделать следующие основные выводы:

1. Исследованы основные методы синтеза процессоров и периферии на кристаллах ПЛИС.

2. Изучены программные среды для создания и отладки устройств в составе ПЛИС.

3. Исследованы и изучены основные аспекты многопроцессорных систем с общей периферией и межпроцессорным доступом.

Полученные результаты позволяют сделать вывод, что на основе разработанных методов может быть реализовано цифровое устройство, в основе которого лежит многопроцессорная система, обеспечивающая обработку цифровых потоков и выполнение заданных алгоритмов.

Таким образом, задачи курсовой работы решены, а поставленная цель достигнута.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

1. Программируемые логические интегральные схемы (ПЛИС) // URL:http://digteh.ru/digital/PLD/ (дата обращения 23.06.2018).

2. Компания ГАММА, электронные компоненты. QUARTUSII // URL:http://www.icgamma.ru/linecard/altera/kits/quartus2/ (дата обращения 22.06.2018).

3. Creating a System with Qsys // URL:https://documentation.altera.com/#/link/mwh1409960181641/mwh140995 8596582 (дата обращения 23.06.2018).

4. Ефремов Н. В., Бородин А. А. Инструментальные средства проектирова- ния и отладки систем на программируемых кристаллах компании Altera: Учебное пособие. М.: Изд-во Московского государственного университета леса, 2012.

5. Spartan-6 Device Handbook // URL:http://www.xilinx.com/support/documentation/user_guides/ug389.pdf (да- та обращения 23.06.2018).