Файл: Мультипроцессоры(ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ).pdf

Добавлен: 14.03.2024

Просмотров: 86

Скачиваний: 0

СОДЕРЖАНИЕ

ГЛАВА 1. ВЫБОР АППАРАТНО-ПРОГРАММНЫХ И ПРОГРАММНЫХ СРЕДСТВ ДЛЯ РАЗРАБОТКИ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ

1.1 ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

1.2. СРЕДСТВО АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ QUARTUSII

1.3. СРЕДА СИСТЕМНОЙ ИНТЕГРАЦИИ QSYS

1.4. ВСТРАИВАЕМЫЙ ПРОЦЕССОР NIOS II

1.5 ВСТРАИВАЕМЫЙ ПРОЦЕССОР MICROBLAZE

1.6. СРЕДСТВО РАЗРАБОТКИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ NIOS II SBT FOR ECLIPSE

ГЛАВА 2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ

2.1. ПРЕИМУЩЕСТВА ИЕРАРХИЧЕСКИХ МНОГОПРОЦЕССОРНЫХ СИСТЕМ

2.2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ NIOS II

2.3. КОНСТРУКЦИИ АППАРАТНЫХ СРЕДСТВ ДЛЯ СОВМЕСТНОГО ИСПОЛЬЗОВАНИЯ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.3.2. АВТОНОМНЫЕ МУЛЬТИПРОЦЕССОРЫ

2.3.3. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ С ОБЩЕЙ ПЕРИФЕРИЕЙ

2.4. ИСПОЛЬЗОВАНИЕ ОБЩИХ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ

2.4.1. РАЗДЕЛЯЕМЫЕ ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА

2.4.2. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПАМЯТИ

2.4.3. ЯДРО АППАРАТНОГО МЬЮТЕКСА

2.4.4. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.5. ПЕРЕКРЫТИЕ АДРЕСНОГО ПРОСТРАНСТВА

2.6. ПРОЕКТИРОВАНИЕ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ДЛЯ НЕСКОЛЬКИХ ПРОЦЕССОРОВ

2.6.1. ПРОГРАММИРОВАНИЕ ПАМЯТИ

Nios II SBT for Eclipse поддерживает отладку программного обеспечения в многопроцессорных системах, позволяя запускать и останавливать несколько сеансов отладки программного обеспечения для одновременно работающих процессоров.

2.3. КОНСТРУКЦИИ АППАРАТНЫХ СРЕДСТВ ДЛЯ СОВМЕСТНОГО ИСПОЛЬЗОВАНИЯ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.3.1. ОСНОВНОЕ РАЗДЕЛЕНИЕ

Многопроцессорные системы Nios II делятся на две основные категории: те, которые разделяют периферийные устройства и те, в которых каждый процессор является автономным и не разделяет периферийные устройства с другими процессорами.

2.3.2. АВТОНОМНЫЕ МУЛЬТИПРОЦЕССОРЫ

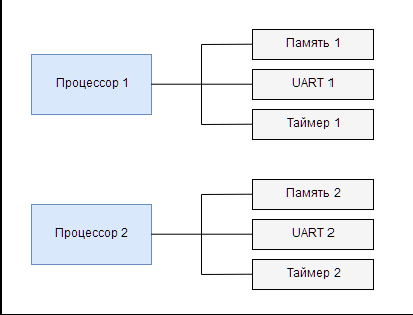

Хотя автономные многопроцессорные системы содержат несколько процессоров, эти процессоры полностью автономны и не общаются друг с другом, как если бы они были полностью отдельными системами. По своей конструкции системы такого типа не используют общие периферийные устройства, и поэтому процессоры не могут мешать друг другу. По- этому такие системы, как правило, менее сложны и создают меньше проблем. На рисунке 4 схематически изображена система из двух автономных процессоров.

Рис. 4. Система из двух автономных процессоров

2.3.3. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ С ОБЩЕЙ ПЕРИФЕРИЕЙ

Многопроцессорные системы, с общими периферийными устройства- ми, могут создавать множество проблем. Для предотвращения этого в Qsys существуют функции, которые позволяют надежно реализовать многопроцессорные системы с общей периферией. Однако создать данную систему не всегда просто.

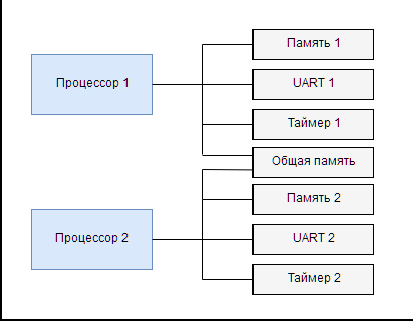

На рисунке 5 показана блок-схема простой многопроцессорной системы, в которой два процессора совместно используют общую память.

На данном рисунке два экземпляра процессоров ис- пользуют, помимо индивидуальной периферии, раздел общей памяти, в котором может находиться их инициализирующее программное обеспечение или их общие данные, которые они могут считывать и переписывать. Сложность данных систем – это обеспечение взаимно исключающего доступа к общей периферии, т.к. одновременное обращение к ней может вызвать повреждении данных и, в худшем случаи, вывести ее из строя.

Рис. 5. Система из двух процессоров с общей памятью

2.4. ИСПОЛЬЗОВАНИЕ ОБЩИХ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ

2.4.1. РАЗДЕЛЯЕМЫЕ ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА

Периферийные устройства считаются разделяемыми, когда к ним могут обращаться несколько процессоров. Панель соединений Qsys определяет, к каким аппаратным компонентам может получить доступ каждый из отдельных процессоров Nios II.

Совместное использование периферийных устройств может быть очень мощной функцией многопроцессорных систем, но нужно заботиться об определении того, какие периферийные устройства системы являются общими, и как различные процессоры взаимодействуют с ними.

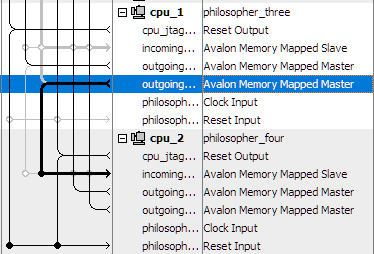

В неиерархической системе периферийные устройства можно сделать общими, просто подключив их к нескольким основным интерфейсам процессора в матрице соединений Qsys. В иерархической системе, периферийные устройства также могут быть доступны для совместного использования с процессорами за пределами подсистемы, содержащей периферийное устройство, экспортируя его интерфейс. Ведущие интерфейсы процессора получают доступ к периферийным устройствам через соединения в матрице соединений Qsys с экспортированными интерфейсами под- системы содержащий периферийное устройство. На рисунке 6 показан пример того, как выглядит соединение двух интерфейсов процессоров в матрице соединений Qsys.

Рис. 6. Пример соединения в матрице соединений Qsys

Основной интерфейс процессора CPU1 может получить доступ к периферийному устройству, расположенному в подсистеме CPU2, посредством соединения с шиной Avalon Memory-Mapped (Avalon-MM) pipeline bridge. Avalon-MM pipeline bridge также обеспечивает механизм для одновременного соединения ведомого интерфейса как к локальному мастер-процессору, так и внешнему ведущему процессору в другом месте иерархии. В этом случае Avalon-MM pipeline bridge экспортирует ведомый, а не ведущий, интерфейс периферии напрямую.

Программное обеспечение, запущенное на каждом процессоре, отвечает за взаимную координацию при доступе к совместно используемым периферийным устройствам с другими процессорами в системе при помощи использования мьютекса. Процессор может взаимодействовать с периферией

взаимно-исключающим доступом одновременно к своему мьютексу и мьютексу соседнего процессора.

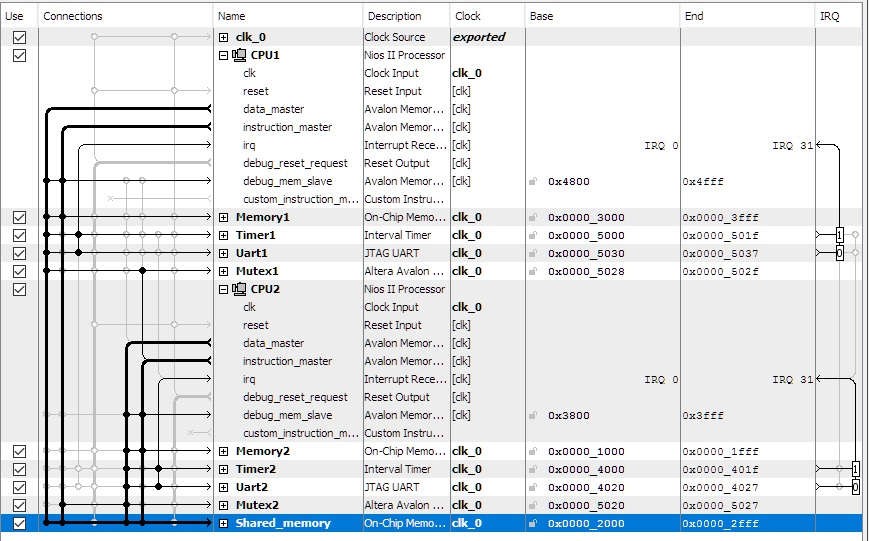

Рис. 7. Совместное использование памяти многопроцессорной системой

На рисунке 7 показана примерная многопроцессорная система, построенная в Qsys. Компонент, указанный снизу, shared_memory (разделенная память), считается разделяемым, потому что ведущие порты данных и команд обоих процессоров подключены к ведомому интерфейсу памяти. Поскольку cpu1 и cpu2 физически способны одновременно записывать блоки данных в совместно используемую память, программное обеспечение для этих процессоров должно использовать мьютексы для защиты целостности данных, хранящихся в общей памяти.

2.4.2. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПАМЯТИ

Наиболее распространенным типом общей периферии в многопроцессорных системах является память. Общая память может использоваться для чего угодно: от простого флага, целью которого является состояние связи между процессорами, до сложных структур данных, которые совместно вычисляются многими процессорами одновременно.

Если компонент памяти должен содержать программную память для нескольких процессоров, то каждый процессор, совместно использующий память, должен использовать отдельную область для инициализации исполняемого кода. Процессоры не могут использовать одну и ту же область памяти для программного пространства. Каждый процессор должен иметь свои собственные уникальные разделы: .text, .rodata, .rwdata, .heap и .stack . Для получения информации о том, как каждый процессор совместно ис- пользует компонент памяти существует программа в выделенной области этой памяти. [9][10]

Если для системы необходим доступ к общему разделу памяти, где хранятся данные, с которыми работают процессоры, то мы должны подключить ведомый интерфейс памяти к ведущим интерфейсам этих процессоров. Все эти соединения необходимо выполнить в иерархическом файле описания верхнего уровня, а не внутри каждой подсистемы отдельно.

Совместное использование памяти данных между несколькими процессорами может быть сложным, поскольку она может работать на запись и на чтение. Если один процессор пишет в определенную область общего доступа, и, в то же время, другой процессор считывает или записывает данные в этой области, то это, вероятно, приведет к повреждению данных, что вызовет ошибки, как минимум, исполняемой программы и, возможно, вызовет сбой всей системы.

Процессоры, использующие общую память или общие интерфейсы, нуждаются в механизме информирования друг друга, чтобы предотвратить их общее воздействие. В следующем разделе описан такой механизм: the Altera hardware mutex core (ядро аппаратного мьютекса). В некоторых случаях ядро мьютекса не обязательно. Например, не требуется мьютекс с односторонним буфером обмена, где только один процессор пишет в буфер, а все остальные процессоры могут работать только в режиме чтения. Однако безопасное совместное использование периферийных устройств без мьютекса возможно, но является более сложным в плане обеспечения взаимно-исключающего доступа.

2.4.3. ЯДРО АППАРАТНОГО МЬЮТЕКСА

Процессор Nios II обеспечивает защиту общих периферийных устройств, обращаясь к ядру аппаратного мьютекса, которое гарантирует, что только один процессор имеет право владения мьютексом в любой момент времени. Ядро аппаратного мьютекса не является внутренней особенностью процессора Nios II. Это простой компонент Qsys.

Термин «мьютекс» означает взаимное исключение. Мьютекс позволяет взаимодействующим процессорам согласовать то, что только один процессор будет получать временный доступ к определенной аппаратной периферии. Это полезно для защиты периферийных устройств от повреждения данных, которые могут появиться при использовать периферийного устройства одновременно несколькими процессорами.

Ядро мьютекса действует как совместно используемое периферийное устройство, предоставляющее собой Atomic тестовую и установочную операцию, которая позволяет процессору проверить, доступен ли мьютекс, и, если это так, завладеть блокировкой мьютекса в одну операцию. Когда процессор завершит работу с совместно используемым периферийным устройством, связанный с мьютексом, процессор освобождает блокировку мьютекса. После этого другой процессор может получить блокировку мьютекса и использовать общую периферию. Без мьютекса такой функции обычно требует процессор для выполнения двух отдельных команд - тестирования и установки, между которыми процессор также может проверить работоспособность и успешность выполнения. В этой ситуации появилось бы два процессора, которые, могли бы определить, что они успешно приобрели взаимоисключающий доступ, хотя это не так.

Ядро мьютекса физически не защищает периферийные устройства в системе от одновременного доступа к ним нескольких процессоров. Программное обеспечение, запущенное на процессорах, несет ответственность за соблюдение правил. Программное обеспечение должно быть написано так, чтобы перед доступом к общему периферийному устройству было необходимо получить мьютекс.

Другой тип мьютекса, называемый программным мьютексом, является общим для многих операционных систем. В компьютерном программировании мьютекс является программным объектом, который позволяет нескольким потокам программ совместно использовать один и тот же ресурс, такой как доступ к файлам, но не одновременно. Когда программа запускается, создается мьютекс с уникальным именем. После этого этапа любой поток, который нуждается в ресурсе, должен блокировать мьютекс из других потоков, пока он использует ресурс. Мьютекс устанавливается для разблокировки, когда данные больше не нужны или процедура завершена. [3][11]

Ядро аппаратного мьютекса является компонентом Qsys с интерфейсом Avalon, который использует логику, чтобы гарантировать, что только одному процессору предоставляется блокировка мьютека в любой момент времени. Пока каждый процессор находится в ожидании соответствующего мьютекса для использования, связанного с ним общего периферийного устройства, это периферийное устройство защищено от повреждений, вызванных одновременным доступом нескольких процессоров. Аппаратное ядро мьютекса само по себе не имеет никакого подключения к общему периферийному устройству; это просто один из видов семафора.

2.4.4. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

Совместное использование периферийных устройств в многопроцессорных системах вызывает некоторые проблемы, обычно приводящих к неэффективному проектированию системы. Самые большие проблемы возникают для периферийных устройств, управляемых прерываниями. Если периферийному устройству разрешено вызывать прерывания у всех процессоров, разделяющих его, нет надежного способа гарантировать, какой процессор ответит первым. Кроме того, если периферийное устройство используется в качестве устройства ввода для нескольких процессоров, становится трудно определить, какой процессор должен собирать данные с устройства. Хотя для этого может быть создана сложная система связей, такая система выходит за рамки настоящего документа и не предоставляет собой абстрактный слой библиотек Nios II (HAL).

При построении любой системы, особенно многопроцессорной системы, рекомендуется только устанавливать соединения между процессорами и периферийными устройствами, которые требуют прямой связи. Напри- мер, если процессор работает и использует только один встроенный чип памяти, нет необходимости подключать этот процессор к любой другой памяти в системе. Физически отключая процессор от памяти, он не взаимодействует с ней, тем самым экономит ресурсы ПЛИС и гарантирует, что процессор никогда не повредит данные хранящиеся в этой памяти.