Файл: Мультипроцессоры(ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ).pdf

Добавлен: 14.03.2024

Просмотров: 73

Скачиваний: 0

СОДЕРЖАНИЕ

ГЛАВА 1. ВЫБОР АППАРАТНО-ПРОГРАММНЫХ И ПРОГРАММНЫХ СРЕДСТВ ДЛЯ РАЗРАБОТКИ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ

1.1 ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

1.2. СРЕДСТВО АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ QUARTUSII

1.3. СРЕДА СИСТЕМНОЙ ИНТЕГРАЦИИ QSYS

1.4. ВСТРАИВАЕМЫЙ ПРОЦЕССОР NIOS II

1.5 ВСТРАИВАЕМЫЙ ПРОЦЕССОР MICROBLAZE

1.6. СРЕДСТВО РАЗРАБОТКИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ NIOS II SBT FOR ECLIPSE

ГЛАВА 2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ

2.1. ПРЕИМУЩЕСТВА ИЕРАРХИЧЕСКИХ МНОГОПРОЦЕССОРНЫХ СИСТЕМ

2.2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ NIOS II

2.3. КОНСТРУКЦИИ АППАРАТНЫХ СРЕДСТВ ДЛЯ СОВМЕСТНОГО ИСПОЛЬЗОВАНИЯ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.3.2. АВТОНОМНЫЕ МУЛЬТИПРОЦЕССОРЫ

2.3.3. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ С ОБЩЕЙ ПЕРИФЕРИЕЙ

2.4. ИСПОЛЬЗОВАНИЕ ОБЩИХ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ

2.4.1. РАЗДЕЛЯЕМЫЕ ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА

2.4.2. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПАМЯТИ

2.4.3. ЯДРО АППАРАТНОГО МЬЮТЕКСА

2.4.4. СОВМЕСТНОЕ ИСПОЛЬЗОВАНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

2.5. ПЕРЕКРЫТИЕ АДРЕСНОГО ПРОСТРАНСТВА

2.6. ПРОЕКТИРОВАНИЕ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ДЛЯ НЕСКОЛЬКИХ ПРОЦЕССОРОВ

2.6.1. ПРОГРАММИРОВАНИЕ ПАМЯТИ

3) Nios II/e (economy) – экономичная версия процессора, требующая наименьшее количество ресурсов кристалла для реализации, и обладающая ограниченным набором возможностей.

Процессор Nios II имеет RISC архитектуру, в которой арифметические и логические операции выполняются над операндами, находящимися в регистрах общего назначения. Обмен информацией между регистрами и па- мятью осуществляется путем выполнения команд “Load” и “Store” (загрузка и хранение соответственно).

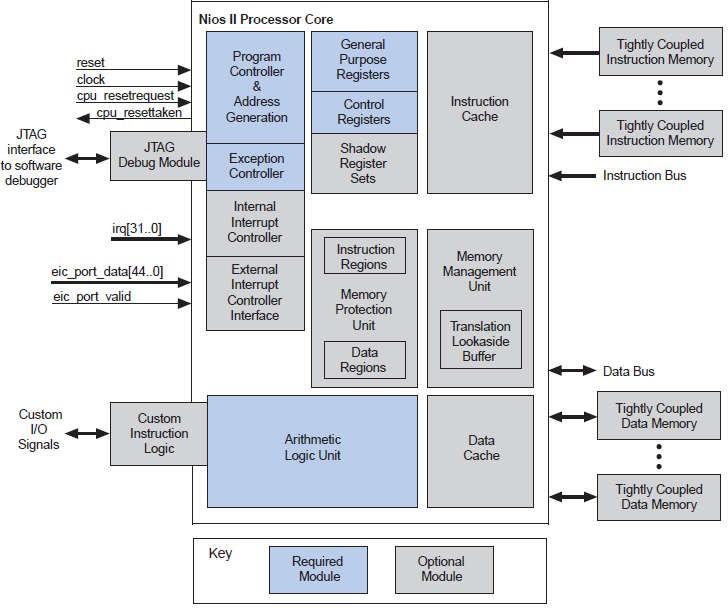

Машинное слово процессора Nios II имеет ширину 32 бита, такой же размер имеют его регистры. Для адресации байтов в слове используется little-endian стиль, при котором менее значимые байты расположены по меньшим адресам в ОП. Процессор имеет гарвардскую архитектуру, то есть использует раздельные шины для данных и команд. Структурная схе- ма процессора Nios II воспроизведена на рисунке 1.

Рис. 1. Структурная схема процессора Nios II.

Процессор Nios II может функционировать в следующих режимах:

1) Режим супервизора. В данном режиме процессору разрешается выполнять все инструкции и осуществлять любые функции. Процессор переключается в этот режим после поступления сигнала сброса;

2) Режим пользователя. Целью данного режима является предотвращение выполнения определенных инструкций системного назначения. Переключение в этот режим становится возможным лишь при наличии модуля управления памятью (MMU) или модуля защиты памяти (MPU).

Ниже приведены основные характеристики процессора Nios II/f:

1) Более 2-х гигабайт адресного пространства;

2) Отдельный кэш инструкций и кэш данных;

3) Аппаратное выполнение умножения и деления;

4) 6-ти стадийный конвейер;

5) Поддержка исключений;

6) Система защиты памяти;

7) Система виртуальной памяти;

8) Выполнение операции умножения и сдвига за один такт;

9) Динамическое предсказание ветвлений;

10) Использование до 256 пользовательских инструкций;

11) Широкие возможности отладки через JTAG модуль;

12) Реализация требует 1400-1800 логических элементов FPGA;

13) Реализация включает 3 блока памяти M4K, плюс блоки для кэш памяти;

14) Производительность процессора 51 миллион операций в секунду (51 DMIPS) на частоте 50 МГц.

Процессор Nios II и интерфейсы для сопряжения с оперативной памятью и другими периферийными компонентами системы реализуются в кристалле ПЛИС. Для соединения компонентов процессорной системы ис- пользуется синхронная шина Avalon. Шина Avalon может содержать сле- дующие типы:

1) Avalon Clock Interface, для передачи синхросигналов и управления ими;

2) Avalon Reset Interface, для передачи сигналов сброса;

3) Avalon Streaming Interface (Avalon-ST), для поддержки однонаправленных потоков данных, включая мультиплексированные, пакетные и данные цифровых сигнальных процессоров;

4) Avalon Memory Mapped Interface (Avalon-MM), для чтения/записи с адресацией типа ведущий/ведомый;

5) Avalon Tri-State Conduit Interface (Avalon TC), для сопряжения с моду- лями вне кристалла;

6) Avalon Interrupt Interface, для реализации приоритетной системы прерываний;

7) Avalon Conduit Interface, для объединения отдельных сигналов или групп сигналов, которые не подходят под любой другой тип шины Avalon.

1.5 ВСТРАИВАЕМЫЙ ПРОЦЕССОР MICROBLAZE

Процессор MicroBlaze представляет собой полнофункциональное программируемое 32-разрядное ядро RISC, оптимизированное для ПЛИС. Он удовлетворяет разнообразным требованиям на промышленных, медицинских, автомобильных, потребительских и коммуникационных инфраструктурных рынках, среди прочих - для чувствительных к стоимости и больших объемов приложений. Он весьма конфигурируемый и может использоваться в качестве микроконтроллера или встроенного процессора в ПЛИС (Spartan-6 или Artix-7 ПЛИС) или в качестве сопроцессора для ARM Cortex-A9 на базе Zynq-7000 AP SoCs. Для оптимизации встраиваемых систем большую роль играет доступность простых в использовании средств разработки и отладки аппаратного и программного обеспечения, времени выполнения и IP ядер. Чтобы решить эту проблему, Xilinx также предоставляет Vivado® Design Suite, который включает в себя IP- интегратор Vivado (IPI) и ISE Embedded edition (для ПЛИС Spartan-6). Эти инструменты обеспечивают среду разработки на базе IP и систем, в которой используются встроенные IP-устройства с поддержкой Plug-and-Play (на базе AXI4) и полный комплект средств разработки программного обеспечения (SDK). Эти компоненты помогают пользователям быстрее создавать более совершенные системы, сокращая общее время разработки решения [5][5].

Несмотря на растущую сложность и изощренность встроенных систем, даже для недорогих приложений с низким уровнем затрат, исключи- тельное время выхода на рынок продолжает расти. Даже низкоуровневые программируемые решения вышли далеко за пределы логики склеивания для полнофункциональных высокоприоритетных компонентов, которые позволяют ключевой системный интеллект посредством встроенной обработки. Наличие правильного программируемого устройства и встроенного процессора больше не является полным решением; в равной степени важно иметь дееспособные программные средства, программное обеспечение времени выполнения, поддержку периферийных IP-адресов и документацию.

Встроенные процессорные системы ПЛИС Xilinx предоставляют разработчику множество исключительных преимуществ по сравнению с типичными микропроцессорами, включая настройку, снижение устаревания, снижение стоимости компонентов и аппаратное ускорение [6][6].

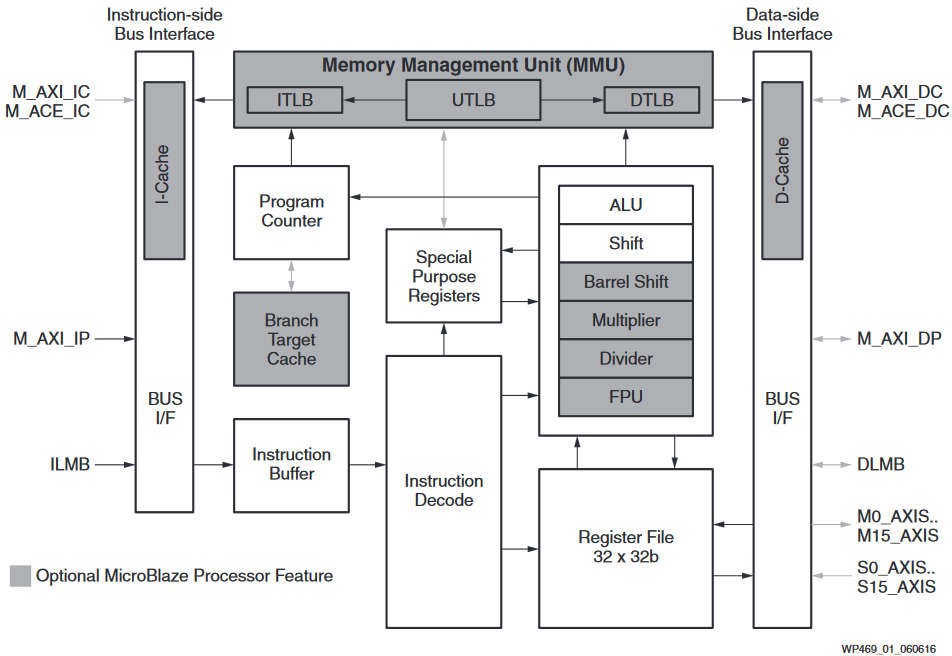

На рисунке 2 представлен структурный вид ядра MicroBlaze

Рис. 2. Структурный вид ядра MicroBlaze

В отличие от готовых процессоров, инструменты проектирования Xilinx поддерживают функции и потоки, такие как Vivado High-Level Synthesis, который позволяет создавать IP-адреса из C / C ++ и SystemC без необходимости вручную писать RTL.

1.6. СРЕДСТВО РАЗРАБОТКИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ NIOS II SBT FOR ECLIPSE

Средство разработки программного обеспечения Nios II (SBT) для Eclipse - это интегрированная среда разработки для задач разработки программного обеспечения Nios II, таких как редактирование, сборка и отладка [7][7].

Основные возможности Nios II SBT for Eclipse это:

1) Инструменты на основе проектов Eclipse;

2) Шаблоны для создания программного обеспечения Nios II;

3) Компилятор для C и C ++ (GNU);

4) Поддержка библиотеки Newlib C;

5) Навигатор источника, редактор и отладчик;

6) Средства создания программного обеспечения;

7) Пакет поддержки пакета поддержки Nios II (BSP);

8) Quartus Prime Programmer;

9) Командная оболочка Nios II;

10) Полная документация и материалы для обучения.

1.7. СЕМЕЙСТВО ПЛИС CYCLONЕ V

Основой массива программируемой логики 28-нм семейства Cyclone V, в отличии от других семейств серии Cyclone, являются адаптивные ло- гические модули (также, как в сериях Arria и Stratix). Кроме этого, микро- схемы семейства Cyclone V содержат блоки цифровой обработки сигналов переменной точности, блоки встроенного ОЗУ, высокоскоростные прие- мопередатчики, аппаратные IP-блоки (контроллеры PCI-Express и кон- троллеры внешней синхронной памяти), и средства защиты проекта от не- санкционированного копирования, и модификации [8][8].

Семейство Cyclone V имеет в своем составе микросхемы, которые со- держат такие инновационные решения, как аппаратный процессорный блок, основой которого является одно- или двухъядерный процессор ARM Cortex A9.

Семейство Cyclone V состоит из следующих подсемейств:

1) Cyclone V E – не содержит встроенных трансиверов и аппаратных кон- троллеров PCI Express;

2) Cyclone V GX – содержит встроенные трансиверы с максимальной ско- ростью передачи данных 3.125 Гбит/с;

3) Cyclone V GT – содержит встроенные трансиверы с максимальной ско- ростью передачи данных 5 Гбит/с;

4) Cyclone V SE – содержит аппаратный процессорный блок (одно- или двухъядерный);

5) Cyclone V SX – содержит двухъядерный аппаратный процессорный блок и встроенные трансиверы с максимальной скоростью передачи данных 3.125 Гбит/с;

6) Cyclone V ST– содержит двухъядерный аппаратный процессорный блок и встроенные трансиверы с максимальной скоростью передачи данных 5 Гбит/с.

Для создания и отладки многопроцессорной системы была выбрана плата разработки представленная на рисунке 3. В основе данной платы ле- жит кристалл Altera Cyclone V 5CEBA4F17C8N.

Рис. 3. Внешний вид платы разработки

ГЛАВА 2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ

2.1. ПРЕИМУЩЕСТВА ИЕРАРХИЧЕСКИХ МНОГОПРОЦЕССОРНЫХ СИСТЕМ

Мультипроцессорные системы обладают преимуществом повышенной производительности, но, почти всегда, обладают большей сложностью их разработки, включающей в себя используемые аппаратные средства и программное обеспечение. Идея использования нескольких процессоров для выполнения различных задач и использования на разных процессорах в режиме реального времени встроенных приложений получила широкую популярность. ПЛИС Altera обеспечивают идеальную платформу для раз- работки встроенных многопроцессорных систем, поскольку аппаратное обеспечение может быть легко модифицировано и настроено, используя инструмент Qsys для обеспечения оптимальной производительности системы. Увеличение возможностей ПЛИС Altera делают возможными системные конструкции со многими процессорами Nios II на одном кристалле. Кроме того, с мощным инструментом интеграции, таким как Qsys, различные конфигурации системы могут быть спроектированы, построены и оценены в короткие сроки. Qsys включает в себя иерархические структуры, снижая сложность системы за счет раздельного проектирования в дискретных подсистемах. Каждая подсистема экспортирует пользовательские интерфейсы, образующих иерархию подсистем.

2.2. МНОГОПРОЦЕССОРНЫЕ СИСТЕМЫ NIOS II

Nios II SBT for Eclipse включает функции, помогающие в создании и отладки многопроцессорных систем. Несколько процессоров Nios II способны эффективно делиться периферией благодаря возможности ввода в систему дружественного арбитража, описанного при помощи Qsys. Поскольку возможности Qsys позволяют практически без усилий добавлять столько процессоров в систему, сколько будет необходимо, основное внимание в создании многопроцессорных систем больше не лежит в организации и подключении отдельных аппаратных компонентов. Задача построения многопроцессорных систем состоит в том, чтобы написать программное обеспечение для этих процессоров, которое позволит им эффективно работать вместе и не противоречить друг другу. [8][9]

Чтобы помочь предотвратить взаимодействие нескольких процессоров друг с другом, в систему, при помощи Qsys, введено ядро аппаратного мьютекса. Ядро аппаратного мьютекса позволяет различным процессорам получать доступ к общим периферийным устройством в течение определенного периода времени. Это временное владение периферией защищает общее периферийное устройство от повреждений при одновременном действии на него нескольких процессоров.

Чтобы предотвратить общее воздействие на периферию, необходимо написать программное обеспечение, которое ждет получения разрешения от мьютекса на подключение к общему периферийному устройству, обеспечивая взаимно-эксклюзивный доступ.

Nonatomic тестовая и установочная операция имеет серьезный риск: два процессора могут одновременно проверить флаг и определить, что ни один процессор не имеет доступа. Если оба процессора подключаются к периферийному устройству, они нарушают взаимное исключение.

Atomic тестовая и установочная операция позволяет избежать этого риска, поскольку её нельзя прерывать. Данная операция позволяет процессору проверять право доступа и приобретать права владения ресурса за одну операцию.

Тот факт, что операция не может быть прервана, также обеспечивает, защиту от переключения системных задач во время тестирования или при- обретения/освобождения мьютекса процессором.

Ядро аппаратного мьютекса обеспечивает семафор для взаимоисключающего доступа к любой периферии. Программное обеспечение определяет это периферийное устройство и отвечает за равномерное использование мьютекса API (англ. интерфейс прикладного программирования) для обеспечения взаимно-исключающего доступа каждый раз, когда периферийное устройство доступно.