Файл: Отчет по лабораторной работе 6 Дисциплина Архитектура вычислительных систем Проектирование конечного автомата.docx

Добавлен: 27.03.2024

Просмотров: 16

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА» (СПбГУТ)

Факультет Инфокоммуникационных сетей и систем (ИКСС)

Кафедра Программной инженерии и вычислительной техники (ПИиВТ)

Отчет по лабораторной работе №6

Дисциплина: Архитектура вычислительных систем

«Проектирование конечного автомата»

Выполнили: студенты группы ИКПИ-03

Шукуров А. А., Мухамадиев А. А.

Приняла: старший преподаватель кафедры ПИиВТ

Неелова Ольга Леонидовна

Санкт-Петербург 2022

Оглавление

| Цель работа | |

| Задание | |

| Диаграмма переходов состояний | |

| Ход работы | |

| Листинг кода | |

| coder.v | |

| lower.v | |

| main.v | |

| cdd.v | |

| Вывод | |

Цель работы

Изучение методов программного проектирования конечных автоматов по выданному заданию на проектирование. Определение количества состояний автомата, условий перехода и действий внутри состояния.

Задание

Последовательный вывод многозначного числа на 6 индикаторов.

Программа использует 4 модуля: main, cdd, coder, lower.

| Модуль | Описание |

| main | Основной (результирующий) модуль, который соединяет все модули |

| cdd | Комбинаторное цифровое устройство |

| coder | Декодировщик данных для дисплея |

| lower | Понижайщий счётчик для понижения такта |

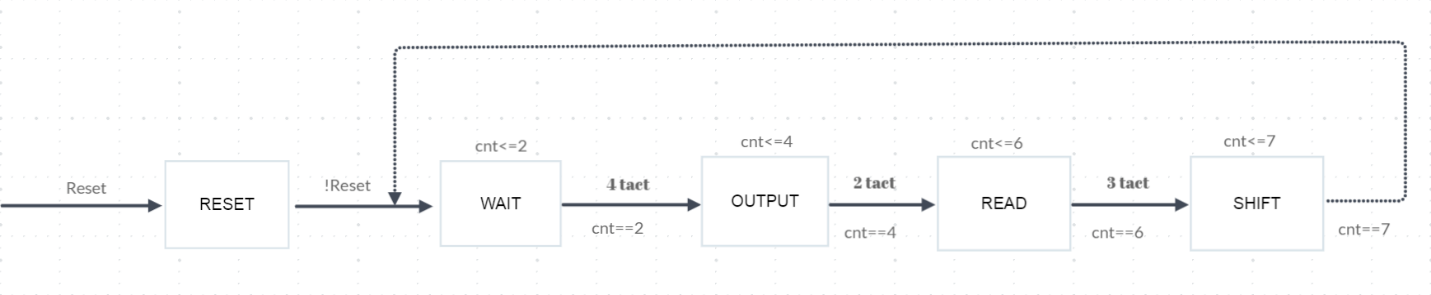

Модуль комбинаторного цифрового устройства используют следующие 4 состояния: RESET, WAIT, OUTPUT, READ, SHIFT. Снизу привидена таблица с описанием каждого состояния.

| Состояние | Описание |

| RESET | Настройка на ноль регистры и счетчик |

| WAIT | Ожидание ввода данных |

| OUTPUT | Вывод данных |

| READ | Чтение данных и вписывание в регистр |

| SHIFT | Сдвиг регистра |

Диаграмма переходов состояний автомата

|

Рисунок 1. Диаграмма переходов состояний автомата.

Ход работы

Сначала были написаны и прокомпилированы программы: coder.v, lower.v – понижающий счетчик, cdd.v – программа, описывающая логику работы автомата (логика смены состояний и логика действий внутри состояний). После этого написана результирующая программа main.v, связывающая три предыдущих узла, проведена ее компиляция.

После выполненной работы в ModelSim файлы coder.v, lower.v, cdd.v и main.v были перенесены в Quartus для реализации автомата на макете FPGA CycloneV, проведена компиляция с файлом main.v как старшим в иерархии.

В PinPlanner была произведено присвоение каждому выводу микросхемы значения вывода проектируемого устройства.

Далее снова была проведена компиляция всех программ с последующим подключением макета FPGA CycloneV к ПК и его программированием через Programmer. После выполнения всех необходимых действий в Programmer’е была нажата кнопка «Start» и проверка работы автомата.

Листинг кода

coder.v

module coder

(in, out);

input[3:0] in;

output[6:0] out;

reg[6:0] code;

assign out=code;

always @* begin

case(in)

4'b0000:code= 7'b1000000;

4'b0001:code= 7'b1111001;

4'b0010:code= 7'b0100100;

4'b0011:code= 7'b0110000;

4'b0100:code= 7'b0011001;

4'b0101:code= 7'b0010010;

4'b0110:code= 7'b0000010;

4'b0111:code= 7'b1111000;

4'b1000:code= 7'b0000000;

4'b1001:code= 7'b0010000;

4'b1010:code= 7'b0001000;

4'b1011:code= 7'b0000011;

4'b1100:code= 7'b1000110;

4'b1101:code= 7'b0100001;

4'b1111:code= 7'b0000110;

endcase

end

endmodule

//

lower.v

module lower

#(parameter N=29, DIV=29'd7500000)

(input wire in, output reg out);

reg[N:0] gen2;

wire[N:0] gen2_next;

wire counter_next;

always@(posedge in)

begin

gen2 <= gen2_next;

out <= out;

if (gen2 == DIV) begin

gen2 <= 0;

out <= out;

end

end

assign gen2_next=gen2 +1'b1;

endmodule

//

cdd.v

module cdd

(clock, reset, data, out0, out1, out2, out3, out4, out5, ledr);

input clock;

input reset;

input [3:0]data;

output reg[3:0] out0;

output reg[3:0] out1;

output reg[3:0] out2;

output reg[3:0] out3;

output reg[3:0] out4;

output reg[3:0] out5;

output [2:0] ledr;

reg [3:0] shift_reg [5:0];

reg [3:0] memory;

reg [3:0] state;

reg [2:0] counter;

assign ledr = counter;

parameter RESET = 0;

parameter WAIT = 1;

parameter OUTPUT = 2;

parameter READ = 3;

parameter SHIFT = 4;

always@(posedge clock or negedge reset) begin

if(!reset)begin

state<=RESET;

end else begin

case (state)

RESET:

state <=WAIT;

WAIT:

if(counter == 3'd2) begin

state<=OUTPUT;

end

OUTPUT:

if(counter == 3'd4) begin

state<=READ;

end

READ:

if(counter == 3'd6) begin

state<=SHIFT;

end

SHIFT:

if(counter == 3'd7) begin

state<=WAIT;

end

endcase

end

end

always@(posedge clock) begin

case (state)

RESET: begin

out0 = 4'd0;

out1 = 4'd0;

out2 = 4'd0;

out3 = 4'd0;

out4 = 4'd0;

out5 = 4'd0;

counter = 3'd0;

end

WAIT: begin

counter <= counter +1;

end

OUTPUT: begin

out0 <= shift_reg[0];

out1 <= shift_reg[1];

out2 <= shift_reg[2];

out3 <= shift_reg[3];

out4 <= shift_reg[4];

out5 <= shift_reg[5];

counter <= counter+1;

end

READ: begin

memory <= data;

counter <= counter +1;

end

SHIFT: begin

shift_reg[0] <= memory;

shift_reg[1] <= shift_reg[0];

shift_reg[2] <= shift_reg[1];

shift_reg[3] <= shift_reg[2];

shift_reg[4] <= shift_reg[3];

shift_reg[5] <= shift_reg[4];

counter = counter +1;

end

endcase

end

endmodule

//

main.v

module main

(clock, reset, data, hex0, hex1, hex2, hex3, hex4, hex5, ledr);

input clock;

input reset;

input [3:0]data;

output [6:0] hex0;

output [6:0] hex1;

output [6:0] hex2;

output [6:0] hex3;

output [6:0] hex4;

output [6:0] hex5;

output [2:0] ledr;

wire low;

wire [3:0] out0;

wire [3:0] out1;

wire [3:0] out2;

wire [3:0] out3;

wire [3:0] out4;

wire [3:0] out5;

lower counter(.in(clock), .out(low));

cdd device(.clock(low), .reset(reset), .data(data), .out0(out0), .out1(out1), .out2(out2), .out3(out3), .out4(out4), .out5(out5));

coder coder0( .in(out0), .out(hex0));

coder coder1( .in(out1), .out(hex1));

coder coder2( .in(out2), .out(hex2));

coder coder3( .in(out3), .out(hex3));

coder coder4( .in(out4), .out(hex4));

coder coder5( .in(out5), .out(hex5));

Вывод

В ходе выполнения работы произведено синтезирование конечного автомата (реализовано на макете FPGA CycloneV) со сменой состояний – вывод многозначного числа на 6 индикаторов последовательно. Были определены состояния машины: начальное (RESET), ожидание ввода данных (WAIT), вывод данных (OUTPUT), перенос в регистр (READ) и сдивг регистра (SHIFT).

Для каждого из состояний были определены и поставлены условия перехода и описаны действия внутри состояний. В результате работы были изучены методы программного проектирования конечных автоматов.

В синтез конечного автомата входило:

программы на VerilogHDL (coder.v, lower.v, cdd.v, main.v) для реализации на макете FPGA CycloneV;

диаграмма переходов состояний автомата (Рисунок 1).