Файл: Методические указания по подготовке к экзамену на повышение квалификации Электромеханик по средствам автоматики и приборам технологического оборудования.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 04.05.2024

Просмотров: 64

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

АЦП последовательного приближения. Типичными значениями является разрядность 12-18 бит при частоте преобразования 100KSPS-1MSPS.

Наибольшей точности достигают сигма-дельта АЦП, имеющие разрядность до 24 бит включительно и скорость от единиц SPS до единиц KSPS.

Еще одним типом АЦП, который находил применение в недавнем прошлом, является интегрирующий АЦП. Интегрирующие АЦП в настоящее время практически полностью вытеснены другими типами АЦП, но могут встретиться в старых измерительных приборах.

АЦП прямого преобразования

АЦП прямого преобразования получили широкое распространение в 1960-1970 годах, и стали производиться в виде интегральных схем в 1980-х. Они часто используются в составе «конвейерных» АЦП (в данной статье не рассматриваются), и имеют разрядность 6-8 бит при скорости до 1 GSPS.

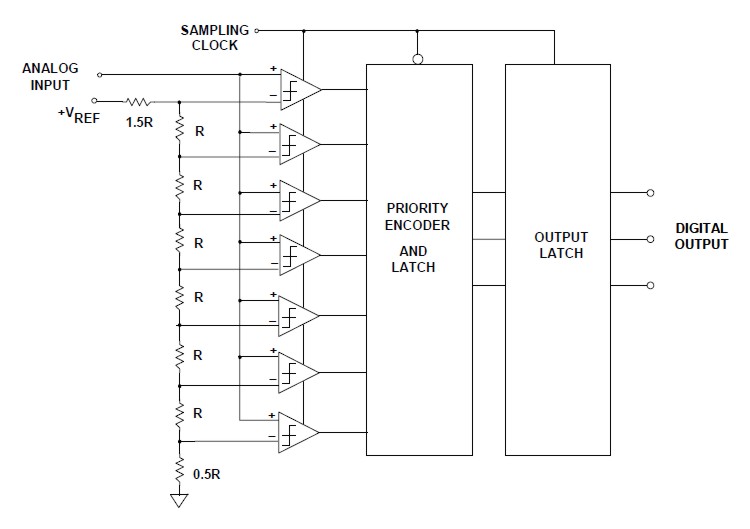

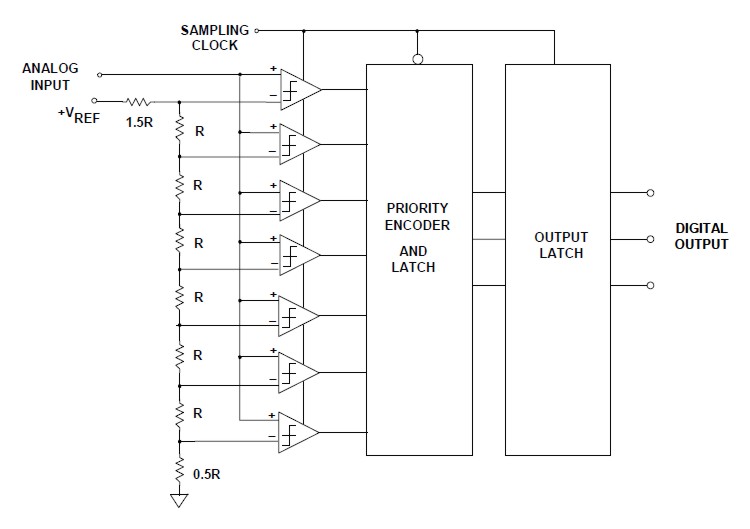

Архитектура АЦП прямого преобразования изображена на рис. 1

Рис. 1. Структурная схема АЦП прямого преобразования

Принцип действия АЦП предельно прост: входной сигнал поступает одновременно на все «плюсовые» входы компараторов, а на «минусовые» подается ряд напряжений, получаемых из опорного путем деления резисторами R. Для схемы на рис. 1 этот ряд будет таким: (1/16, 3/16, 5/16, 7/16, 9/16, 11/16, 13/16) Uref, где Uref – опорное напряжение АЦП.

Пусть на вход АЦП подается напряжение, равное 1/2 Uref. Тогда сработают первые 4 компаратора (если считать снизу), и на их выходах появятся логические единицы. Приоритетный шифратор (priority encoder) сформирует из «столбца» единиц двоичный код, который фиксируется выходным регистром.

Теперь становятся понятны достоинства и недостатки такого преобразователя. Все компараторы работают параллельно, время задержки схемы равно времени задержки в одном компараторе плюс время задержки в шифраторе. Компаратор и шифратор можно сделать очень быстрыми, в итоге вся схема имеет очень высокое быстродействие.

Но для получения N разрядов нужно 2^N компараторов (и сложность шифратора тоже растет как 2^N). Схема на рис. 1. содержит 8 компараторов и имеет 3 разряда, для получения 8 разрядов нужно уже 256 компараторов, для 10 разрядов – 1024 компаратора, для 24-битного АЦП их понадобилось бы свыше 16 млн. Однако таких высот техника еще не достигла.

АЦП последовательного приближения

АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий еще к Фибоначчи. В своей книге «Liber Abaci» (1202 г.) Фибоначчи рассмотрел «задачу о выборе наилучшей системы гирь», то есть о нахождении такого ряда весов гирь, который бы требовал для нахождения веса предмета минимального количества взвешиваний на рычажных весах. Решением этой задачи является «двоичный» набор гирь.

Аналого-цифровой преобразователь последовательного приближения (SAR, Successive Approximation Register) измеряет величину входного сигнала, осуществляя ряд последовательных «взвешиваний», то есть сравнений величины входного напряжения с рядом величин, генерируемых следующим образом:

1. на первом шаге на выходе встроенного цифро-аналогового преобразователя устанавливается величина, равная 1/2Uref (здесь и далее мы предполагаем, что сигнал находится в интервале (0 – Uref).

2. если сигнал больше этой величины, то он сравнивается с напряжением, лежащим посередине оставшегося интервала, т.е., в данном случае, 3/4Uref. Если сигнал меньше установленного уровня, то следующее сравнение будет производиться с меньшей половиной оставшегося интервала (т.е. с уровнем 1/4Uref).

3. Шаг 2 повторяется N раз. Таким образом, N сравнений («взвешиваний») порождает N бит результата.

Рис. 2. Структурная схема АЦП последовательного приближения.

Таким образом, АЦП последовательного приближения состоит из следующих узлов:

1. Компаратор. Он сравнивает входную величину и текущее значение «весового» напряжения (на рис. 2. обозначен треугольником).

2. Цифро-аналоговый преобразователь (Digital to Analog Converter, DAC). Он генерирует «весовое» значение напряжения на основе поступающего на вход цифрового кода.

3. Регистр последовательного приближения (Successive Approximation Register, SAR). Он осуществляет алгоритм последовательного приближения, генерируя текущее значение кода, подающегося на вход ЦАП. По его названию названа вся данная архитектура АЦП.

4. Схема выборки-хранения (Sample/Hold, S/H). Для работы данного АЦП принципиально важно, чтобы входное напряжение сохраняло неизменную величину в течение всего цикла преобразования. Однако «реальные» сигналы имеют свойство изменяться во времени. Схема выборки-хранения «запоминает» текущее значение аналогового сигнала, и сохраняет его неизменным на протяжении всего цикла работы устройства.

Достоинством устройства является относительно высокая скорость преобразования: время преобразования N-битного АЦП составляет N тактов. Точность преобразования ограничена точностью внутреннего ЦАП и может составлять 16-18 бит (сейчас стали появляться и 24-битные SAR ADC, например, AD7766 и AD7767).

1.15 Топология сетей

Топологии сетей

К средствам измерения и преобразования измерительной информации в АСУТП относятся измерительные преобразователи, расположенные на 1-м нижнем уровне системы. Первичные измерительные преобразователи позволяют системе получать информацию о состоянии технологического процесса, на основании которой впоследствии принимаются решения об управляющих воздействиях. Передающие измерительные преобразователи служат для преобразования измерительной информации в сигналы, удобные для обработки и передачи на расстояние.

Главной особенностью средств измерения, применяемых в АСУТП, является то, что первичный преобразователь конструктивно объединяется с передающим в измерительном преобразователе, называемом датчик. Все датчики на выходе вырабатывают электрические сигналы. Кроме того, в целях унификации последующих уровней системы по возможности применяют средства измерений, вырабатывающие стандартные выходные сигналы, или цифровые коды, удобные для дальнейшей передачи.

В современных АСУТП применяются два класса контроллеров: программируемые логические контроллеры и РС-совместимые контроллеры.

Программируемый логический контроллер (ПЛК). Это микропроцессорное устройство, предназначенное для управления технологическими процессами в промышленности и другими сложными технологическими объектами. Принцип работы контроллера заключается в сборе сигналов от датчиков и их обработке по прикладной программе пользователя с выдачей управляющих сигналов на исполнительные устройства.

Основными функциональными элементами контроллеров являются:

корпус;

источник питания;

процессорный модуль;

модули ввода-вывода (модули УСО);

модули связи и интерфейсов;

специализированные модули.

Источник питания должен обеспечивать непрерывность и надежность работы всех узлов контроллера. Особое внимание уделяется наличию резервного источника питания (как правило, аккумуляторная батарея), который позволяет сохранять информацию при отключении внешнего электропитания.

Модуль процессора в зависимости от используемой элементной базы может быть 8-, 16- и 32-разрядным. Объем оперативной памяти существенно различается в различных моделях контроллеров: от десятков килобайт до десятков мегабайт. По логическому построению модуль процессора контроллера аналогичен системному блоку персонального компьютера, где вместо дисковых накопителей в контроллерах используются перепрограммируемые запоминающие устройства и flash-память. В некоторых моделях контроллеров flash-память отсутствует, в других — может достигать десятков, а иногда и сотен мегабайт. В модуле процессора встроены также часы реального времени.

Наибольшей точности достигают сигма-дельта АЦП, имеющие разрядность до 24 бит включительно и скорость от единиц SPS до единиц KSPS.

Еще одним типом АЦП, который находил применение в недавнем прошлом, является интегрирующий АЦП. Интегрирующие АЦП в настоящее время практически полностью вытеснены другими типами АЦП, но могут встретиться в старых измерительных приборах.

АЦП прямого преобразования

АЦП прямого преобразования получили широкое распространение в 1960-1970 годах, и стали производиться в виде интегральных схем в 1980-х. Они часто используются в составе «конвейерных» АЦП (в данной статье не рассматриваются), и имеют разрядность 6-8 бит при скорости до 1 GSPS.

Архитектура АЦП прямого преобразования изображена на рис. 1

Рис. 1. Структурная схема АЦП прямого преобразования

Принцип действия АЦП предельно прост: входной сигнал поступает одновременно на все «плюсовые» входы компараторов, а на «минусовые» подается ряд напряжений, получаемых из опорного путем деления резисторами R. Для схемы на рис. 1 этот ряд будет таким: (1/16, 3/16, 5/16, 7/16, 9/16, 11/16, 13/16) Uref, где Uref – опорное напряжение АЦП.

Пусть на вход АЦП подается напряжение, равное 1/2 Uref. Тогда сработают первые 4 компаратора (если считать снизу), и на их выходах появятся логические единицы. Приоритетный шифратор (priority encoder) сформирует из «столбца» единиц двоичный код, который фиксируется выходным регистром.

Теперь становятся понятны достоинства и недостатки такого преобразователя. Все компараторы работают параллельно, время задержки схемы равно времени задержки в одном компараторе плюс время задержки в шифраторе. Компаратор и шифратор можно сделать очень быстрыми, в итоге вся схема имеет очень высокое быстродействие.

Но для получения N разрядов нужно 2^N компараторов (и сложность шифратора тоже растет как 2^N). Схема на рис. 1. содержит 8 компараторов и имеет 3 разряда, для получения 8 разрядов нужно уже 256 компараторов, для 10 разрядов – 1024 компаратора, для 24-битного АЦП их понадобилось бы свыше 16 млн. Однако таких высот техника еще не достигла.

АЦП последовательного приближения

АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий еще к Фибоначчи. В своей книге «Liber Abaci» (1202 г.) Фибоначчи рассмотрел «задачу о выборе наилучшей системы гирь», то есть о нахождении такого ряда весов гирь, который бы требовал для нахождения веса предмета минимального количества взвешиваний на рычажных весах. Решением этой задачи является «двоичный» набор гирь.

Аналого-цифровой преобразователь последовательного приближения (SAR, Successive Approximation Register) измеряет величину входного сигнала, осуществляя ряд последовательных «взвешиваний», то есть сравнений величины входного напряжения с рядом величин, генерируемых следующим образом:

1. на первом шаге на выходе встроенного цифро-аналогового преобразователя устанавливается величина, равная 1/2Uref (здесь и далее мы предполагаем, что сигнал находится в интервале (0 – Uref).

2. если сигнал больше этой величины, то он сравнивается с напряжением, лежащим посередине оставшегося интервала, т.е., в данном случае, 3/4Uref. Если сигнал меньше установленного уровня, то следующее сравнение будет производиться с меньшей половиной оставшегося интервала (т.е. с уровнем 1/4Uref).

3. Шаг 2 повторяется N раз. Таким образом, N сравнений («взвешиваний») порождает N бит результата.

Рис. 2. Структурная схема АЦП последовательного приближения.

Таким образом, АЦП последовательного приближения состоит из следующих узлов:

1. Компаратор. Он сравнивает входную величину и текущее значение «весового» напряжения (на рис. 2. обозначен треугольником).

2. Цифро-аналоговый преобразователь (Digital to Analog Converter, DAC). Он генерирует «весовое» значение напряжения на основе поступающего на вход цифрового кода.

3. Регистр последовательного приближения (Successive Approximation Register, SAR). Он осуществляет алгоритм последовательного приближения, генерируя текущее значение кода, подающегося на вход ЦАП. По его названию названа вся данная архитектура АЦП.

4. Схема выборки-хранения (Sample/Hold, S/H). Для работы данного АЦП принципиально важно, чтобы входное напряжение сохраняло неизменную величину в течение всего цикла преобразования. Однако «реальные» сигналы имеют свойство изменяться во времени. Схема выборки-хранения «запоминает» текущее значение аналогового сигнала, и сохраняет его неизменным на протяжении всего цикла работы устройства.

Достоинством устройства является относительно высокая скорость преобразования: время преобразования N-битного АЦП составляет N тактов. Точность преобразования ограничена точностью внутреннего ЦАП и может составлять 16-18 бит (сейчас стали появляться и 24-битные SAR ADC, например, AD7766 и AD7767).

1.15 Топология сетей

Топологии сетей

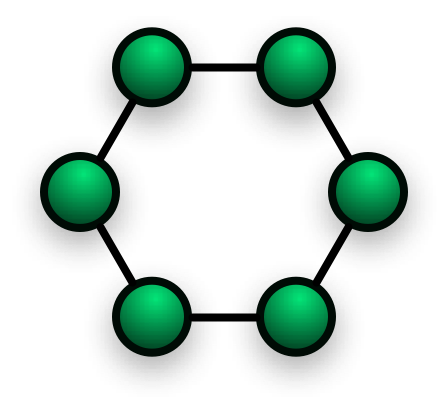

| Сетевая топология (от греч. τόπος, - место) — способ описания конфигурации сети, схема расположения и соединения сетевых устройств. Топология – это схема соединения каналами связи компьютеров или узлов сети между собой. Сетевая топология может быть

Существует множество способов соединения сетевых устройств. Выделяют следующие топологии:

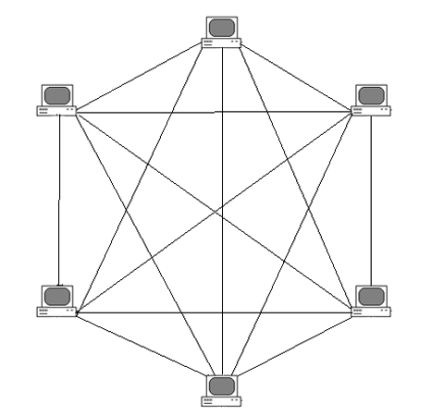

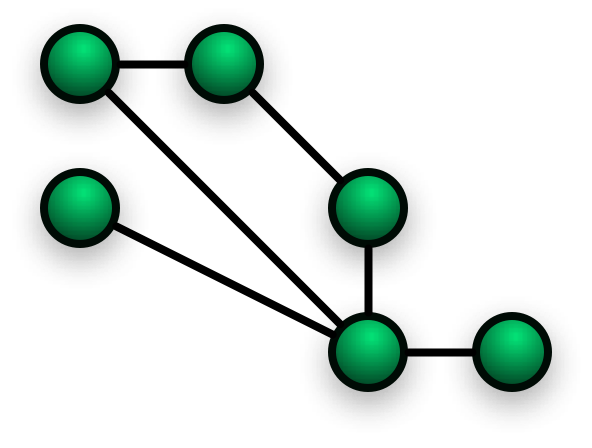

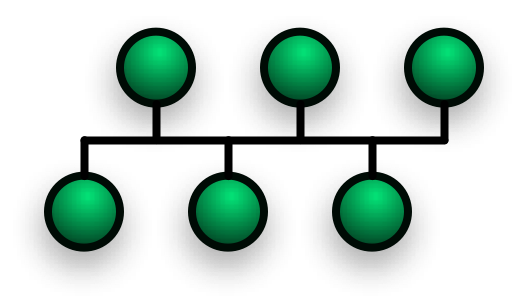

Рассмотрим каждую из них по подробнее. 1) Полносвязная топология — топология компьютерной сети, в которой каждая рабочая станция подключена ко всем остальным. Этот вариант является громоздким и неэффективным, несмотря на свою логическую простоту. Для каждой пары должна быть выделена независимая линия, каждый компьютер должен иметь столько коммуникационных портов сколько компьютеров в сети. По этим причинам сеть  может иметь только сравнительно небольшие конечные размеры. Чаще всего эта топология используется в многомашинных комплексах или глобальных сетях при малом количестве рабочих станций. Технология доступа в сетях этой топологии реализуется методом передачи маркера. Маркер – это пакет, снабженный специальной последовательностью бит (его можно сравнить с конвертом для письма). Он последовательно предается по кольцу от компьютера к компьютеру в одном направлении. Каждый узел ретранслирует передаваемый маркер. Компьютер может передать свои данные, если он получил пустой маркер. Маркер с пакетом передается, пока не обнаружится компьютер, которому предназначен пакет. В этом компьютере данные принимаются, но маркер движется дальше и возвращается к отправителю. После того, как отправивший пакет компьютер убедится, что пакет доставлен адресату, маркер освобождается. Недостаток: громоздкий и неэффективный вариант, т.к. каждый компьютер должен иметь большое кол-во коммуникационных портов. 2) Ячеистая топология - базовая полносвязная топология компьютерной сети, в которой каждая рабочая станция сети соединяется с несколькими другими рабочими станциями этой же сети. Характеризуется высокой отказоустойчивостью, сложностью настройки и переизбыточным расходом кабеля. Каждый компьютер имеет множество возможных путей соединения с другими компьютерами. Обрыв кабеля не приведёт к потере соединения между двумя компьютерами.  Получается из полносвязной путем удаления некоторых возможных связей. Эта топология допускает соединение большого количества компьютеров и характерна, как правило, для крупных сетей. 3) Общая шина, представляет собой общий кабель (называемый шина или магистраль), к которому подсоединены все рабочие станции. На концах кабеля находятся терминаторы, для предотвращения отражения сигнала. Сравнение с другими топологиями. Достоинства:

Недостатки:

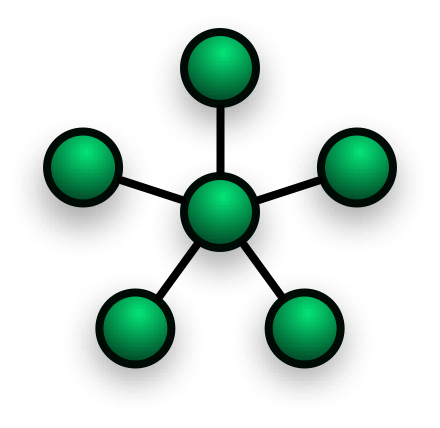

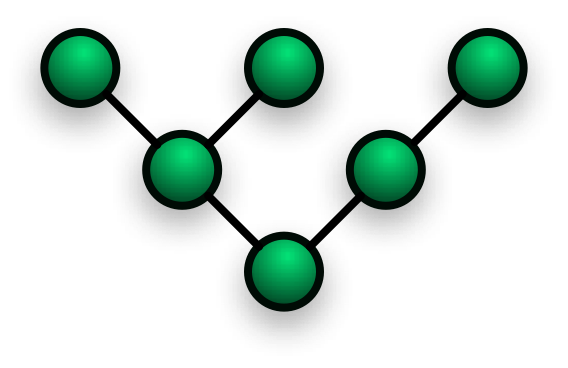

Шинная топология представляет собой топологию, в которой все устройства локальной сети подключаются к линейной сетевой среде передачи данных. Такую линейную среду часто называют каналом, шиной или трассой. Каждое устройство, например, рабочая станция или сервер, независимо подключается к общему шинному кабелю с помощью специального разъема. Шинный кабель должен иметь на конце согласующий резистор, или терминатор, который поглощает электрический сигнал, не давая ему отражаться и двигаться в обратном направлении по шине. 4) Звезда - базовая топология компьютерной сети, в которой все компьютеры сети присоединены к центральному узлу (обычно коммутатор), образуя физический сегмент сети. Подобный сегмент сети может функционировать как отдельно, так и в составе сложной сетевой топологии (как правило, «дерево»). Весь обмен информацией идет исключительно через центральный компьютер, на который таким способом возлагается очень большая нагрузка, поэтому ничем другим, кроме сети, он заниматься не может. Как правило, именно центральный компьютер является самым мощным, и именно на него возлагаются все функции по управлению обменом. Никакие конфликты в сети с топологией звезда в принципе невозможны, потому что управление полностью централизовано.  Метод доступа реализуется с помощью технологии Arcnet. Этот метод доступа также использует маркер для передачи данных. Маркер передается от компьютера к компьютеру в порядке возрастания адреса. Как и в кольцевой топологии, каждый компьютер регенерирует маркер. Сравнение с другими топологиями. Достоинства:

Недостатки:

5) Кольцо - это топология, в которой каждый компьютер соединен линиями связи только с двумя другими: от одного он только получает информацию, а другому только передает. На каждой линии связи, как и в случае звезды, работает только один передатчик и один приемник. Это позволяет отказаться от применения внешних терминаторов. Работа в сети кольца заключается в том, что каждый компьютер ретранслирует (возобновляет) сигнал, то есть выступает в роли повторителя, потому затухание сигнала во всем кольце не имеет никакого значения, важно только затухание между соседними компьютерами кольца. Четко выделенного центра в этом случае нет, все компьютеры могут быть одинаковыми. Однако достаточно часто в кольце выделяется специальный абонент, который управляет обменом или контролирует обмен. Понятно, что наличие такого управляющего абонента снижает надежность сети, потому что выход его из строя сразу же парализует весь обмен.  Компьютеры в кольце не являются полностью равноправными (в отличие, например, от шинной топологии). Одни из них обязательно получают информацию от компьютера, который ведет передачу в этот момент, раньше, а другие — позже. Именно на этой особенности топологии и строятся методы управления обменом по сети, специально рассчитанные на «кольцо». В этих методах право на следующую передачу (или, как еще говорят, на захват сети) переходит последовательно к следующему по кругу компьютеру. Подключение новых абонентов в «кольцо» обычно совсем безболезненно, хотя и требует обязательной остановки работы всей сети на время подключения. Как и в случае топологии «шина», максимальное количество абонентов в кольце может быть достаточно большое (1000 и больше). Кольцевая топология обычно является самой стойкой к перегрузкам, она обеспечивает уверенную работу с самыми большими потоками переданной по сети информации, потому что в ней, как правило, нет конфликтов (в отличие от шины), а также отсутствует центральный абонент (в отличие от звезды). В кольце, в отличие от других топологий (звезда, шина), не используется конкурентный метод посылки данных, компьютер в сети получает данные от стоящего предыдущим в списке адресатов и перенаправляет их далее, если они адресованы не ему. Список адресатов генерируется компьютером, являющимся генератором маркера. Сетевой модуль генерирует маркерный сигнал (обычно порядка 2—10 байт во избежание затухания) и передает его следующей системе (иногда по возрастанию MAC-адреса). Следующая система, приняв сигнал, не анализирует его, а просто передает дальше. Это так называемый нулевой цикл. Последующий алгоритм работы таков — пакет данных GRE, передаваемый отправителем адресату начинает следовать по пути, проложенному маркером. Пакет передаётся до тех пор, пока не доберётся до получателя. Сравнение с другими топологиями. Достоинства:

Недостатки:

6) Снежинка (Иерархическая Звезда или древовидная топология) - топология типа звезды, но используется несколько концентратов, иерархически соединенных между собой связями типа звезда. Топология "снежинка" требует меньшей длины кабеля, чем "звезда", но больше элементов.  Самый распространенный способ связей как в локальных сетях, так и в глобальных. 1.16 Средства измерения в составе автоматизированной системы управления технологическим процессом |

К средствам измерения и преобразования измерительной информации в АСУТП относятся измерительные преобразователи, расположенные на 1-м нижнем уровне системы. Первичные измерительные преобразователи позволяют системе получать информацию о состоянии технологического процесса, на основании которой впоследствии принимаются решения об управляющих воздействиях. Передающие измерительные преобразователи служат для преобразования измерительной информации в сигналы, удобные для обработки и передачи на расстояние.

Главной особенностью средств измерения, применяемых в АСУТП, является то, что первичный преобразователь конструктивно объединяется с передающим в измерительном преобразователе, называемом датчик. Все датчики на выходе вырабатывают электрические сигналы. Кроме того, в целях унификации последующих уровней системы по возможности применяют средства измерений, вырабатывающие стандартные выходные сигналы, или цифровые коды, удобные для дальнейшей передачи.

В современных АСУТП применяются два класса контроллеров: программируемые логические контроллеры и РС-совместимые контроллеры.

Программируемый логический контроллер (ПЛК). Это микропроцессорное устройство, предназначенное для управления технологическими процессами в промышленности и другими сложными технологическими объектами. Принцип работы контроллера заключается в сборе сигналов от датчиков и их обработке по прикладной программе пользователя с выдачей управляющих сигналов на исполнительные устройства.

Основными функциональными элементами контроллеров являются:

корпус;

источник питания;

процессорный модуль;

модули ввода-вывода (модули УСО);

модули связи и интерфейсов;

специализированные модули.

Источник питания должен обеспечивать непрерывность и надежность работы всех узлов контроллера. Особое внимание уделяется наличию резервного источника питания (как правило, аккумуляторная батарея), который позволяет сохранять информацию при отключении внешнего электропитания.

Модуль процессора в зависимости от используемой элементной базы может быть 8-, 16- и 32-разрядным. Объем оперативной памяти существенно различается в различных моделях контроллеров: от десятков килобайт до десятков мегабайт. По логическому построению модуль процессора контроллера аналогичен системному блоку персонального компьютера, где вместо дисковых накопителей в контроллерах используются перепрограммируемые запоминающие устройства и flash-память. В некоторых моделях контроллеров flash-память отсутствует, в других — может достигать десятков, а иногда и сотен мегабайт. В модуле процессора встроены также часы реального времени.