ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 03.02.2024

Просмотров: 22

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

ФЕДЕРАЛЬНОЕ АГЕНСТВО ЖЕЛЕЗНОДОРОЖНОГО

ТРАНСПОРТА

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«Петербургский государственный университет путей сообщения

Императора Александра I»

(ФГБОУ ВО ПГУПС)

Ярославский филиал ПГУПС

КУРСОВАЯ РАБОТА

Дисциплина: Электроника

Специализация: 25.05.05 Системы обеспечения движения поездов

Специальность: «Автоматика и телемеханика на транспорте

Форма обучения – ЗАОЧНАЯ

Вариант 11

Группа: АТ-07-006

Выполнил: Смирнов И.В.

Преподаватель: Сульдин В.И.

г.Ярославль

2023

Содержание

Введение 3

1. Описание АЦП последовательного приближения 5

2. Расчет элементов схемы управляющего задающего таймера для АЦП К1113ПВ1. 13

2.1. Расчет уапрвляющего задающего таймера на микросхеме КР1006ВИ1. 15

2.2. Моделирование схемы управляющего задающего таймера для АЦП-К1113ПВ1. 16

3 Расчет преобразователя уровней (ПУ) 18

3.1 Расчетные параметры: 18

3.2 Логический элемент КМПД серия К176 19

3.3 Логический элемент ТТЛШ серия К1533. 19

3.4 Выбор схемы преобразователя уровней. 20

3.5 Выбор биполярного транзистора. 23

3.6 Расчёт схемы преобразователя уровней в заданном температурном диапазоне и выбор номиналов резисторов. 24

Заключение 28

Литература 29

Введение

При построении цифровых систем управления и контроля, в частности с использованием микропроцессоров (МП), используют устройства аналого-цифрового (АЦП) и цифро-аналогового (ЦАП) преобразований. ЦАП используют в большинстве АЦП как в режиме аналого-цифрового, так и цифро-аналогового преобразований; кроме того, в цифровых системах связи и передачи данных (модемы, кодеры), оконечных устройствах цифровых телевизионных и космических линий связи, активных

фильтрах с управляемой полосой пропускания, усилителях с программируемым коэффициентом усиления, испытательной и измерительной технике [1].

АЦП находят применение в микропроцессорных информационных и управляющих системах. Роль этих устройств может быть пояснена с помощью рис. 1, где обозначено:

Рисунок 1 - Применение АЦП в микропроцессорных информационных и управляющих системах.

ОУ - объект управления; Д - датчики, преобразующие измеряемые величины в электрическое напряжение; АЦП - аналого-цифровой преобразователь; ЦСОИ - цифровая система обработки информации (МП); ЦАП - цифро-аналоговый преобразователь; ИУ - исполнительное устройство, формирующее сигналы управления.

АЦП производит преобразование аналогового сигнала, имеющего бесконечное множество значений, в сигнал с конечным множеством значений (квантование по уровню), а также его временную дискретизацию, т. е. преобразование сигнала, описываемого функцией непрерывного времени, в сигнал, представляемый функцией дискретного времени.

Курсовая работа посвящена вопросам применения интегральных микросхем на аналого-цифровых преобразователях (АЦП), которые нашли применение в цифровых системах связи, в автоматизированных системах, в различной радиоаппаратуре, согласно задания – шифр 11.

Таблица 1

| Последняя цифра учебного шифра | Тип АЦП, основная интегральная микросхема |

| 1 | АЦП последовательного приближения с К572 ПВ1 |

Таблица 2

| Параметр | Вторая цифра учебного шифра |

| 1 | |

| Частота, ГЦ |  |

| Скважность | 5 |

| Длительность фронтов, мкс, не более |  |

| Амплитуда, В | 4 |

Таблица 3

| Первая цифра учебного шифра | Согласуемые элементы серии ИМС | Нагрузочная способность ПУ | Частота переключения F, МГц | Температурный диапазон, оС |

| 1 | ТТЛ-КМДП К176-К531 | 3 | 1 | +10÷45 |

1. Описание АЦП последовательного приближения

Структурная схема АЦП последовательного приближения приведена на рис. 1.

Рис. 1 Структурная схема АЦП.

АЦП состоит из:

-

генератора тактовых импульсов ГТИ, состоящего из микросхемы DD1, резисторов R1-R3, конденсатора С1 и диодов VD1-VD2

-

компаратора напряжения КН, включающего DA1 и R4

-

логического элемента ЛЭ (в схемной реализации необходимости в нём не возникло)

-

сдвигового регистра RG, в качестве которого используется DD2

-

8-разрядного цифро-аналогового преобразователя ЦАП, представленного микросхемой DD4

-

регистра хранения RG, включающего микросхему DD3.

Принципиальная электрическая схема, построенная в соответствии со структурной схемой, приведена на рис. 2.

Рис. 2 Принципиальная электрическая схема АЦП.

Алгоритм работы схемы таков. Нулевой тактовый импульс с ГТИ устанавливает выход 12 микросхемы DD2 в низкое состояние, остальные выходы – в высокое состояние. В результате на выход ЦАП (DD4) подаётся код 01111111, на его выходе формируется напряжение, равное половине преобразуемого диапазона входных напряжений. Компаратор DA1 сравнивает его с входным напряжением, и если входное напряжение превышает напряжение с выхода ЦАП, на его выходе удерживается высокое напряжение. Следующим тактовым импульсом это высокое состояние записывается в триггер с выходом 12 регистра сдвига и остаётся там до самого конца преобразования. Если входное напряжение меньше половины диапазона преобразователя, в триггер с выходом 12 запишется низкое логическое состояние. По окончании второго тактового импульса на выходе регистра сдвига появится значение х0111111 (х – записанное на предыдущем такте значение выхода 12). В результате входное напряжение будет сравниваться с 3/4 преобразуемого диапазона напряжений (при условии, что на 12 выходе высокий уровень). И так далее до тех пор, пока не будет сформирован младший разряд с выходом 1. Если микросхема регистра сдвига используется не на все 12 разрядов, то вход сброса ER (для организации циклических измерений) следует соединять с (12 – n) выходом. При 9-м по счёту тактовом импульсе на выходе (12 – 8 = 4) установится низкое состояние, которое со следующим тактовым импульсом сбросит микросхему. А в момент появления низкого уровня на выходе 4 DD2 этот импульс, предварительно проинвертированный, подаётся на вход С записи регистра хранения DD3. Если инвертирование не производить, то запись в регистр DD3 произойдёт в момент сброса регистра сдвига.

Микросхемы, из которых составлен АЦП, описаны ниже. Их условные графические обозначения приведены на рис. 3.

Рис. 3 Условно-графические обозначения микросхем.

Микросхема К554СА3 является компаратором напряжения с прямым (выв.3) и инверсным (выв.4) входами, входами баланса (выв.7) и стробирования (выв.8), выходным транзисторным каскадом с выходами К (коллектор, выв.9) и Э (эмиттер, выв.2). Она осуществляет сравнение напряжений на прямом и инвертированном входе. При превышении первого над вторым транзистор выходного каскада открывается.

Микросхема К1554ЛН1 представляет собой 6 инверторов со стандартной нагрузочной способностью выходов.

Микросхема К155ИР17 – специальный регистр, предназначенный для построения аналогово-цифровых преобразователей, работающих по принципу последовательного приближения с числом разрядов 12 и менее. Имеет четыре входа: С – для подачи тактовых импульсов (срабатывание триггера происходит по фронту тактовых импульсов), D – для подачи запоминаемой регистром информации, Е – разрешения преобразования и ER – сброса. Работает микросхема следующим образом: при подачи на вход ER низкого уровня по фронту очередного импульса на входе С происходит начальная установка триггеров регистра, т.е. на выходе  устанавливается низкий уровень, на выходах 1-12 – высокий уровень. На выходе окончания преобразования Р появляется высокий уровень. Такое состояние триггера будет сохраняться до тех пор, пока на входе ER удерживается низкий уровень.

устанавливается низкий уровень, на выходах 1-12 – высокий уровень. На выходе окончания преобразования Р появляется высокий уровень. Такое состояние триггера будет сохраняться до тех пор, пока на входе ER удерживается низкий уровень.

После установки на входе сброса высокого уровня первый фронт тактового импульса на входе С произведёт запись в триггер регистра с выходами 12 информации со входа D и установит выход 11 в низкое состояние, на выходах 1-10 и Р будет высокое состояние. Очередной тактовый импульс произведёт запись информации со входа D в очередной триггер регистра и установит следующий за ним выход в низкое состояние. Таким образом, на выходах регистра поочерёдно появляется низкий уровень, вслед за ним - информация со входа D.

После записи информации в последний триггер регистра (с выходом 1) на выходе Р появится низкий уровень, и это состояние триггера зафиксируется до появления низкого уровня на входе сброса ER. Если его соединить с выходом Р, появление низкого уровня на выходе Р по фронту тактового импульса приведёт к установлению исходного состояния регистра. В результате микросхема будет повторять описанный цикл работы с периодом 13 импульсов.

Так микросхема работает при низком уровне на входе Е. Если на вход разрешения преобразования Е подать высокий уровень, то выходы 1-12 и Р переходят в высокое состояние и на сигналы на других входах не реагируют.

Микросхема позволяет использовать её в качестве регистра последовательного приближения и с меньшим, чем на 12, числом разрядов. Для этого на вход ER следует подавать сигналы с выходов 11-1 (в обратном порядке, т.е. чем меньше разрядность, тем выше номер выхода).

Микросхема MAX5102 является 8-разрядным двухканальным цифро-аналоговым преобразователем с объединёнными цифровыми входами и общим опорным напряжением. Выбор канала осуществляется подачей разных уровней на вход А0 (А0 = 0 – первый канал, А0 = 1 – второй канал), запись данных – при низком логическом уровне на входе WR. Если на этом входе удерживается низкий уровень, то данные с цифровых входов попадают на управляющую логику соответствующего канала. Есть так же вход перевода в состояние с пониженным энергопотреблением (SLP). Точность преобразования составляет ± один младший разряд, ток потребления от источника 0,2 мА, скорость преобразования – 6 мкс. Диапазон питающего напряжения +2,7…+5,5В, максимальное опорное равно верхнему значению питающего напряжения.

Микросхема КР1533ИР23 – 8-разрядный регистр хранения информации, тактируемый импульсом, с возможностью перевода выходов в высокоимпедансное состояние. Запись информации в триггеры регистра происходит при подаче фронта тактового импульса на вход С, в этом случае сигналы на выходах регистра повторяют входные, регистр запоминает состояние на входах D0-D7. При подаче постоянного сигнала любого уровня на вход С регистр остаётся в режиме хранения информации. Выходы микросхемы находятся в активном состоянии, если на вход ЕО подан логический нуль. Если же на вход подать логическую единицу, выходы регистра переходят в высокоимпедансное состояние. Сигнал на входе ЕО не влияет на запись в регистр.

Описание микросхемы К572ПВ1

Микросхема К572ПВ1 представляет собой 12-разрядный преобразователь напряжения в двоичный код. В комплекте с внешнем ОУ (компаратором), источником опорного напряжения UОП и генератором тактовых импульсов микросхема выполняет функции АЦП последовательного приближения с параллельным двоичным кодом на выходах.

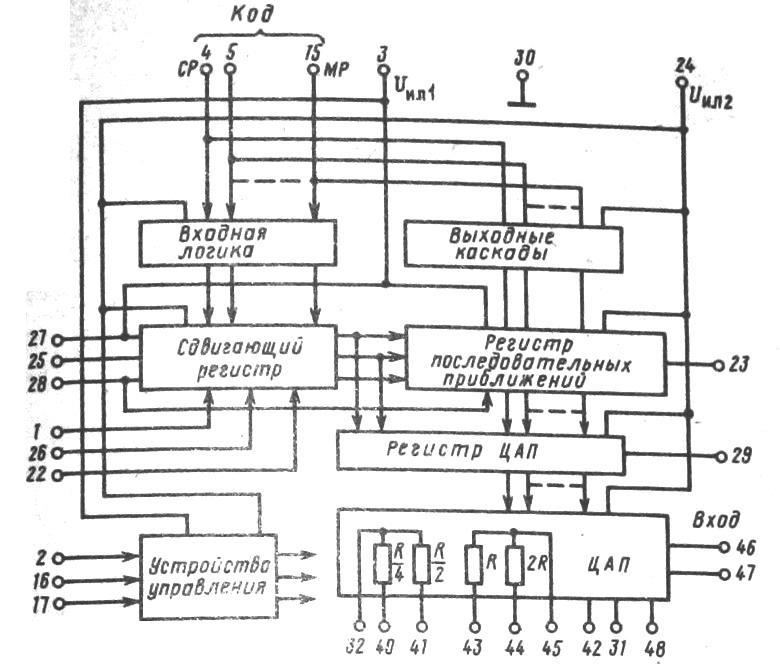

Функциональная схема АЦП показана на рис. 4. Аналоговая часть включает ЦАП, подобный К572ПА1, дополнительные резисторы R/4, R/2, R, 2R для использования с ОУ и на аналоговых входах. Цифровая часть содержит сдвигающий регистр последовательного приближения, регистр ЦАП и устройство управления.

Назначение выводов ИС:

генератора тактовых импульсов ГТИ, состоящего из микросхемы DD1, резисторов R1-R3, конденсатора С1 и диодов VD1-VD2

компаратора напряжения КН, включающего DA1 и R4

логического элемента ЛЭ (в схемной реализации необходимости в нём не возникло)

сдвигового регистра RG, в качестве которого используется DD2

8-разрядного цифро-аналогового преобразователя ЦАП, представленного микросхемой DD4

регистра хранения RG, включающего микросхему DD3.

| 1 – последовательный вход 2 – входы управления СР 3 – напряжение питания UИП1 4-15 – цифровые входы (выходы) 16 – вход управления МР 17 – вход управления режимом Р 22 – выход «цикл» 23 – вход сравнения 24 – напряжение питания UИП2 25 – вход ТИ 26 – выход «конец преобразования» 27 – вход «запуск» 28 – вход «цикл» 29 – вход стробирования ЦАП 30 – цифровая земля 31 – конечный вывод матрицы R-2R | 32 – общий вывод резисторов R1, R2 40 – вывод резистора R1 41 – вывод резистора R2 42 – опорное напряжение 43 – аналоговый вход 1 44 – аналоговый вход 2 45 – общий вывод резисторов аналоговых входов 1, 2 46 – аналоговый выход 1 47 – аналоговый выход 2 48 – аналоговая земля |

Устройство управления обеспечивает следующие режимы работы микросхемы: АЦП, ЦАП, раздельное управление старшими и младшими разрядами, хранение информации в регистре ЦАП. Управление режимами осуществляется в соответствии с табл. 1.

На рис. 5 показан вариант включения АЦП, обеспечивающий повышенную точность и стабильность преобразования. В АЦП имеется дополнительный буферный усилитель ОУ1, напряжение АЦП и входное напряжение сравниваются на ОУ2.

Преобразователь может работать в режиме сравнения токов АЦП и входного сигнала на компараторе ОУ1. При этом обеспечивается максимальное быстродействие. Для включения АЦП в этом режиме необходимо вывод ОУ соединить непосредственно с выводом 23, на вывод 43 подать UВХ, вывод 40 соединить с выводом 44. Включение резисторов R/2 и 2R на входе ОУ1 позволяет изменять UВХ от 0,5UОП до 2UОП. Полярность UВХ может быть любой и определяется полярностью UОП.

Рис. 4 Функциональная схема АЦП.

Таблица 1 Режимы работы микросхемы.

| Режим | Информационно-цифровые разряды | Входы управления | Вход строб | |||

| СР | МР | Р | ||||

| АЦП | 1…12 | 1 | 1 | 0 | 1 | |

| 1…4 | 1 | 0 | 0 | |||

| 5…12 | 0 | 1 | 0 | |||

| разомкнуты | 0 | 0 | 0 | |||

| ЦАП | 1…12 | 1 | 1 | 1 | 1 | |

| 1…4 | 0 | 1 | 1 | |||

| 5…12 | 1 | 0 | 1 | |||

| Хранение информации в регистре ЦАП | − | − | − | − | 0 | |