ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 03.02.2024

Просмотров: 24

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Основные параметры преобразователя

При следующих значениях входных данных:

UИП1 = 5 В, UИП2 = 15 В, UОП = 10,24 В, U0ВЫХ = 0,4 В, U1ВЫХ = 2,4 В,

fТ = 250 кГц

δЛ = ± 0,05%, δЛД = ± 0,1% для КР572ПВ1А;

δД = ±0,1%, δЛД = ± 0,2% для КР572ПВ1Б;

δД = ±0,2%, δЛД = ± 0,4% для КР572ПВ1В;

δПШ = ± 122 ед. МР;

tСРБ = 170 мкс.

Преобразователь может работать в режиме ЦАП. Микросхема переводится в режим ЦАП при подаче напряжения высокого уровня на вывод 17. Запись информации осуществляется подачей на вывод 25 сдвоенного импульса при наличии напряжения низкого уровня на выводе 27. При подаче сдвоенного импульса на вывод 25 и напряжения высокого уровня на вывод 27 информация стирается. Запоминание информации происходит при подаче на вывод 29 напряжения высокого уровня. Для ввода информации в последовательном коде он подаётся на вывод 1 синхронно со сдвоенными импульсами на выводе 25, начиная с МР.

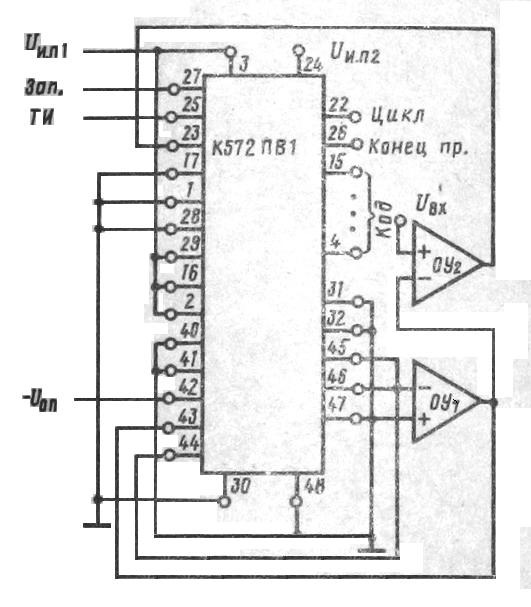

Рис. 5 Включение АЦП.

Преобразователь согласуется с ТТЛ ИС при UИП1 = 5 В ± 5% и с КМДП ИС при UИП1 = 15 В ± 5%. Микросхема может быть согласована с восьмиразрядной шиной данных микропроцессорной системы. Выходы имеют три устойчивых состояния. При работе с микросхемой необходимо соблюдать последовательность включения напряжений и меры защиты.

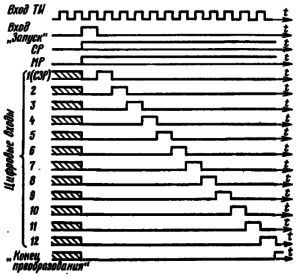

Временные диаграммы работы микросхемы К572ПВ1 (А-В) в режиме АЦП изображены на рисунке 6. Заштрихованы области неопределенного состояния выходов. Напряжение на входе сравнения (вывод 23) U1вк.к = 0

Рис.6. Временные диаграммы работы микросхемы К572ПВ1 (А-В) в режиме АЦП.

2. Расчет элементов схемы управляющего задающего таймера для АЦП К1113ПВ1.

Частота управляющего задающего таймера f0 = 50 кГц, скважность 5.

Выберем для проектирования управляющего задающего таймера микросхему КР1006ВИ1 [2] – рис.7, рис.8.

Выбор микросхемы обосновывается тем, что эта схема представляет собой аналог широко использующейся за рубежом ИС однотактного таймера 555 (по номеру серии первого производителя). Эта микросхема специально предназначена для построения различных высокостабильных импульсных генераторов и таймеров [2,5]. Особо следует отметить высокое быстродействие ИМ, что позволяет проектировать автогенераторы и ждущие генераторы (импульсные) с фронтами до нескольких наносекунд и получать на выходе импульсные сигналы с большой скважностью S≥200 [5]. По количеству областей применения эта интегральная микросхема может конкурировать даже со стандартными операционными усилителями. Остановимся несколько подробнее на её описании структуры и технических характеристик.

Микросхема представляет собой времязадающее устройство (таймер), формирующее импульсы напряжения длительностью от нескольких микросекунд до десятков минут. Выполнена на биполярных транзисторах с изоляцией p-n переходом. Предназначена для применения в стабильных датчиках времени, генераторах импульсов, широтно-импульсных и фазовых модуляторах, преобразователях напряжения, ключевых схемах, преобразователях сигналов, исполнительных устройствах. Корпус типа 2101.8-1 Масса не более 1г.

Функциональный состав: 1 – компаратор напряжения; 2- триггер; 3 – выходной усилитель.

Рисунок 7 - Функциональная схема К1006ВИ1

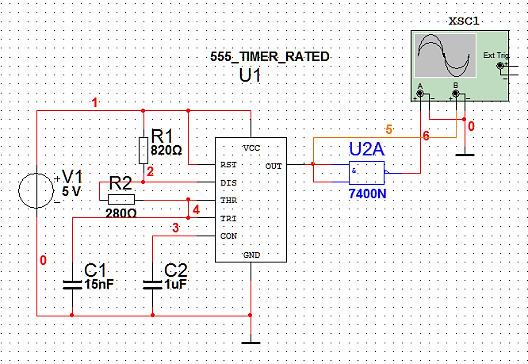

Приведём ниже принципиальную схему управляющего задающего таймера, выполненную на базе микросхемы КР1006ВИ1 – рис.8.

Рисунок 8 - Принципиальная схема генератора импульсов на микросхеме КР1006ВИ1 в режиме автогенерации

При этом:

;

;  - не более10 МОм при Uп=15В и не более 3 Мом при Uп=5В.

- не более10 МОм при Uп=15В и не более 3 Мом при Uп=5В. 2.1. Расчет уапрвляющего задающего таймера на микросхеме КР1006ВИ1.

Скважность есть отношение периода к длине импульса и по условию = 5, заданная частота управляющего задающего таймера

.

.Период

тогда учитывая, что скважность = 5 имеем:

тогда учитывая, что скважность = 5 имеем:

Исходя из соотношений:

;

; .

.Приняв С1 = 15 нФ рассчитаем номиналы сопротивлений:

;

;Выберем из стандартного ряда Е96 типа С3-23±5%

R2 = 280 Ом, R1 = 820 Ом.

Выберем из стандартного ряда конденсаторы типа К73–9-25±5%

С1 = 15 нФ, С2 = 1 мкФ.

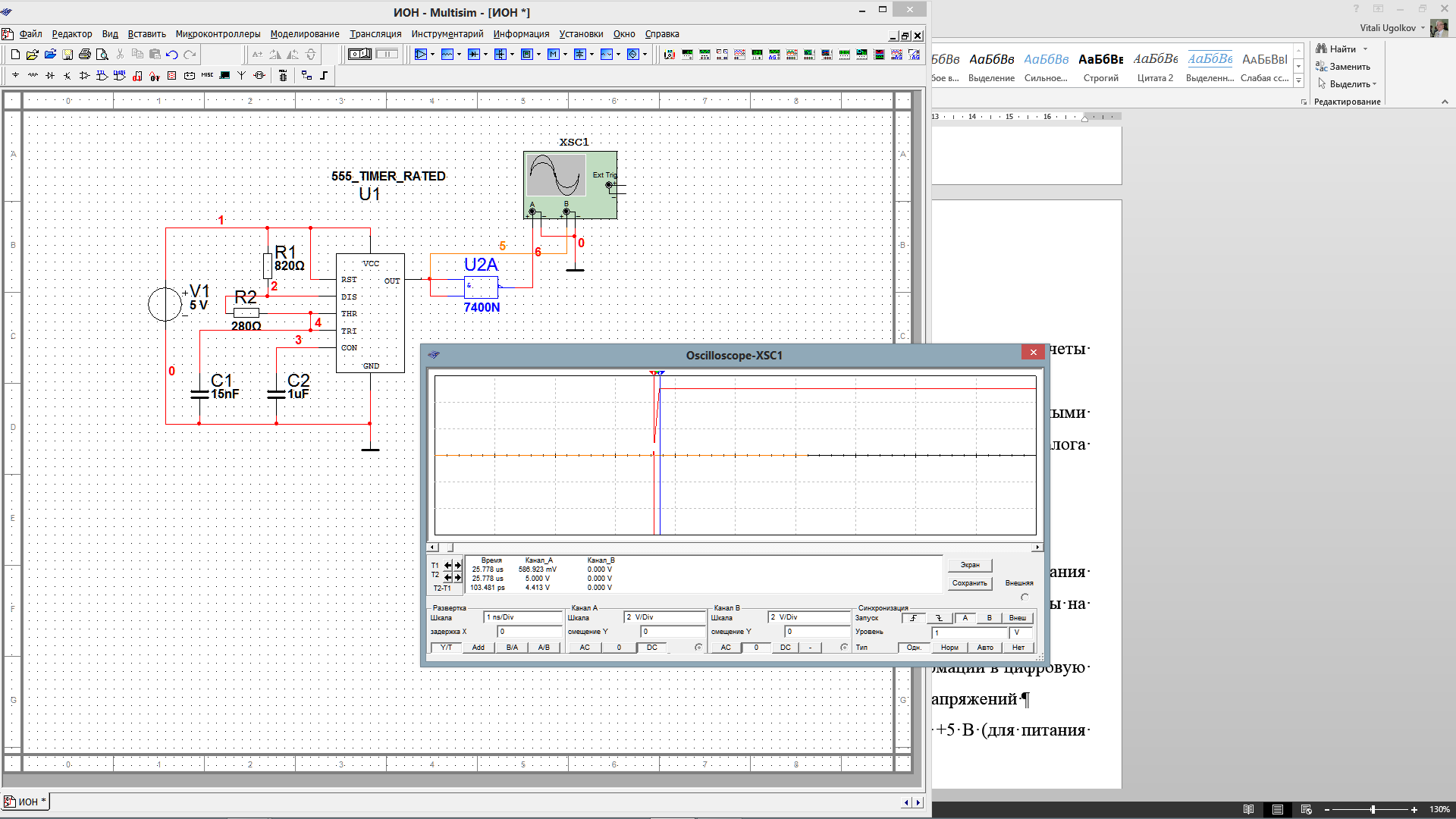

2.2. Моделирование схемы управляющего задающего таймера для АЦП-К1113ПВ1.

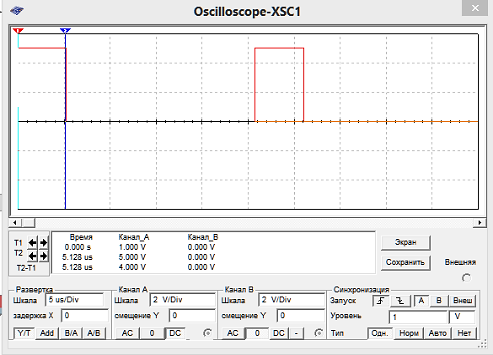

Проверим правильность расчета величин элементов управляющего мультивибратора собранного на микросхеме таймера КР1006ВИ1. Для этого используем систему моделирования электронных схем Multisim 10.

Рисунок 9– Модель схемы управляющего таймера К1006ВИ1 –

аналог NE555.

Рисунок 10 – Временная диаграмма работы схемы управляющего таймера К1006ВИ1 – аналог NE555, основной период Т≈25 мкс, длительность импульса Т1≈5 мкс и соответственно скважность равна 25/5=5.

Скважность выходного сигнала с таймера равна 5, что с высокой точностью соответствует заданной.

Рисунок 11 – Измерение длительности фронта сигнала управляющего таймера К1006ВИ1, длительность фронта Тф≈0,1 мкс.

Получилась длительность фронта Тф≈0,1 мкс<0,5 мкс, что соответствует заданию.

Исходя из данных моделирования можно сделать выводы, что расчеты величин элементов произведены правильно.

Небольшое различие в длительности импульсов объясняется различными характеристиками микросхем К1006ВИ1 и модели её зарубежного аналога NE555..

3 Расчет преобразователя уровней (ПУ)

3.1 Расчетные параметры:

Согласуемые элементы серии ИMC: ТТЛШ(К1533)>КМДП(K176):

-

Нагрузочная способность ПУ: 2 -

Частота переключения f, МГц: 1 -

Температурный диапазон, °С: -10 ÷ 70 -

Монтажная емкость

-

входная емкость элементов .

.

Преобразователи уровней (ПУ) — специальные элементы цифровых устройств, предназначенные для обеспечения совместимости уровней цифровых элементов различных серий. Иногда ПУ называют транслятором уровней.

При проектировании микроэлектронной аппаратуры на цифровых интегральных микросхемах (ИМС) на практике возникает необходимость в совместном использовании цифровых ИМС различных серий. Эти ИМС могут существенно различаться как конструктивно-технологическими, схемотехническими решениями, так и электрическими параметрами, вследствие чего они не могут сопрягаться непосредственно. ПУ позволяет обеспечить управление интегральным логическим элементом (ЛЭ) одной серии с помощью интегрального логического элемента другой серии, т. е. добиться электрического и временного сопряжении этих двух элементов.

и

и  — входное и выходное напряжения;

— входное и выходное напряжения;  и

и  — уровни логической 1 и логического 0;

— уровни логической 1 и логического 0;  — входные и выходные токи ЛЭ в состояниях логического 0 и логической 1 по входу и выходу;

— входные и выходные токи ЛЭ в состояниях логического 0 и логической 1 по входу и выходу;  — допустимая статическая помеха на нулевом уровне (помехозащищенность снизу) и

— допустимая статическая помеха на нулевом уровне (помехозащищенность снизу) и  — допустимая статическая помеха на единичном уровне (помехозащищенность сверху).

— допустимая статическая помеха на единичном уровне (помехозащищенность сверху).В отличие от логических элементов, у которых значения уровней входных и выходных сигналов, как правило, совпадают, у ПУ значения входных и выходных сигналов всегда различны. Это характерный признак ПУ. Поэтому простейшим способом обеспечения полного сопряжения уровней ЛЭ1 и ЛЭ2 является способ построения схемы, при котором входной каскад ПУ - П1 был реализован аналогично схеме выходного каскада ЛЭ1. Аналогично выходной каскад ПУ - ПЗ должен быть реализован по схеме входного каскада ЛЭ2. Чтобы обеспечить выполнение этих условий при таком способе построения ПУ необходимо одновременно использовать питающие напряжения как ЛЭ1, так и ЛЭ2.

В практических случаях, когда ЛЭ1, ПУ, ЛЭ2 размещены на одной и той же плате или в одном корпусе микросхемы, схему ПУ можно упростить, исключив из нее каскады П1 или ПЗ или оба. В интегральном варианте ПУ может содержать все три каскада П1-П2-ПЗ, так как при этом ограничения на соединения между ПУ и цифровыми ИС с ЛЭ будут такими же, как для связей между цифровыми ИС в данной аппаратуре. Это в определенной степени облегчит конструирование электронных блоков аппаратуры.

3.2 Логический элемент КМПД серия К176

Тип логики: НСТЛМ (дополняющие МОП структуры);

Состав серии: К176ЛА7 – четыре элемента 2ИЛИ-НЕ;

Напряжение питания:

;

;Входной ток уровня логического нуля:

;

Входной ток уровня логической единицы:

;

;Выходной ток уровня логического нуля:

;

;Выходной ток уровня логической единицы:

;

;Выходное напряжение логического нуля:

;

;Выходное напряжение логической единицы:

;

;Время задержки переключения с нуля на единицу:

;

;Время задержки переключения с единицы на ноль:

;

;Коэффициент разветвления по выходу:

Температурный диапазон:

;

;3.3 Логический элемент ТТЛШ серия К1533.

Тип логики: ТТЛШ.

Состав серии: К1533ЛА1 – два элемента 4И-НЕ;

Напряжение питания:

;

;Входной ток уровня логического нуля:

;

;Входной ток уровня логической единицы:

;

;Выходной ток уровня логического нуля:

;

;Выходной ток уровня логической единицы:

;

;Выходное напряжение логического нуля:

;

;Выходное напряжение логической единицы:

;

;Время задержки переключения с нуля на единицу:

;

;Время задержки переключения с единицы на ноль:

;

;Коэффициент разветвления по выходу:

;

;Температурный диапазон:

;

;3.4 Выбор схемы преобразователя уровней.