ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 19.03.2024

Просмотров: 25

Скачиваний: 0

2. Розробка структурної та функціональної схем пристрою

-

Розробка структурної схеми пристрою

Необхідний пристрій повинен вимірювати тривалість позитивних імпульсів. Його робота буде полягати в наступному: при подачі сигналу з генератора детектор переднього фронту виявляє передній фронт імпульсу, що дозволяє проходження сигналів тактової частоти на лічильник, який підраховує їх кількість. В цей час детектор заднього фронту відслідковує сигнал на наявність закінчення позитивного імпульсу. Після чого розробляє сигнал, який забороняє проходження імпульсів генератора до лічильника. В лічильнику фіксується код тривалості вимірюваного інтервалу, який подається на блок індикації і послідовно передається в двійково-десятковому коді в пристрій обробки. Якщо тривалість тимчасового інтервалу більше діапазону вимірювання, виробляється сигнал помилки, який виводиться на панелі відображення. Якщо помилки не сталося, на індикаторі відображається вміст лічильника і величина вимірюваного інтервалу передається в пристрій обробки.

До складу пристрою входять елементи:

Начало формы

Конец формы

– детектори фронтів(ДПФ, ДЗФ);

– блок підрахунку тактових імпульсів;

– блок генерації тактових імпульсів;

– блок виводу;

– блок відображення;

– блок управління.

2.2 Розробка функціональної схеми пристрою

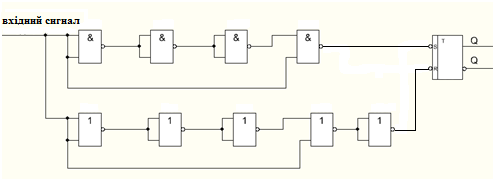

Детектор фронтів складається з двох ланцюжків логічних елементів. Перший з яких – ланцюжок з чотирьох елементів І-НЕ – детектор переднього фронту, призначений для виділення переднього фронту імпульсу і перемикання тригера в одиничний стан. Ланцюжок з елементів АБО-НЕ відстежує задній фронт імпульсу і перемикає тригер у нульовий стан, а також подає імпульс для скидання лічильника. Схеми ланцюжків детекторів фронтів забезпечують надійне перемикання тригера.

Схема вимірювання тривалості позитивних імпульсів складається з логічного елемента «І», а також лічильника. Логічний елемент «І» пропускає тактові імпульси від генератора через подільник частоти, тільки в тому випадку, якщо тригер знаходиться в одиничному стані. Лічильник забезпечує підрахунок імпульсів тактового генератора протягом всього вимірювального імпульсу.

Схема блоку індикації містить регістр зберігання, перетворювач коду, дешифратор та індикатори. Використання регістра дозволяє уникнути мерехтіння під час підрахунку. Запис в регістр виконується тільки по закінченню підрахунку тривалості позитивного імпульсу. Перетворювач коду необхідний для перетворення двійково-десяткового коду з вагами 5121 в двійковий код. Дешифратор необхідний для перетворення двійкового коду в код для індикатора.

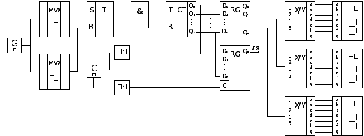

Рисунок 5 - Функціональна схема проектованого пристрою.

Схема

блоку виводу складається з здвигового

регістру, який забезпечує перетворення

паралельного коду в послідовний і

передачу його в канал зв'язку.

Схема

блоку виводу складається з здвигового

регістру, який забезпечує перетворення

паралельного коду в послідовний і

передачу його в канал зв'язку.

До складу тактового генератора входить генератор прямокутних імпульсів заданої частоти і подільник частоти, що забезпечує передачу в ЛЗ із заданою швидкістю, для здвигового регістру.

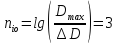

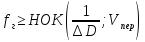

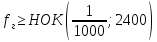

Визначимо розрядність індикаторного пристрою по формулі:

,

,

де Dmax — максимальне значення вимірюваної величини;

ΔD — точність вимірювання.

,

,

Для скорочення кількості елементів при побудові вимірювача часових інтервалів в якості лічильника для підрахунку тактових сигналів використовуємо двійково-десятковий лічильник, що працює у відповідності з кодом обміну з пристроєм обробки. Такий лічильник буде містити 3 послідовно включених однорозрядних двійково-десяткових лічильників. Кількість двійкових розрядів лічильника визначимо за формулою:

Розрядність регістра з паралельним введенням і послідовним виводом інформації визначимо виходячи з того, що для відображення кожного десяткового розряду потрібно 4 біта:

Розділ

3. Розробка принципової схеми пристрою

Розділ

3. Розробка принципової схеми пристрою

3.1 Вибір елементної бази

При розробці пристрою використовуємо інтегральні мікросхеми серії КР1533. Малопотужні інтегральні мікросхеми цієї серії призначені для організації високошвидкісного обміну і обробки цифрової інформації, тимчасового і електричного узгодження сигналів в обчислювальних системах.

Мікросхеми серії КР1533(74ALS - зарубіжний аналог), споживають енергію на 1 біт в 20 разів меншу, ніж у старих серіях. Мікросхеми виготовляються за вдосконаленою епітаксійно-планарною технологією. У мікросхемах використані інтегральні транзистори Шотткі з дуже малим об'ємом колекторної області, чим реалізовано практично граничну швидкодію.

Щоб зберегти значну навантажувальну здатність при безпечній щільності колекторного струму, вхідний струм низького рівня зменшений до 0,2 мА(замість 1,6 мА для К155). В схему логічного елементу додано емітерний повторювач.

Технічні характеристики:

-

стандартні ТТЛ рівні сигналів;

-

напруга живлення 5,0 В ±10%;

-

затримка на вентиль 4 нс;

-

потужність споживання на вентиль 1 мВт;

-

тактова частота до 70 МГц;

-

вихідний струм навантаження низького рівня до 24 мА;

-

вихідний струм навантаження високого рівня до 15 мА;

-

гарантовані статистичні і динамічні характеристики при ємності навантаження 50 пФ у діапазоні температур до +70°С і напруг живлення 5 В ±10%;

-

стійкість до статичної електрики до 200 В;

-

широкий набір типономіналів мікросхем.

3.2

Проектування

схем

виділення фронтів часового інтервалу

3.2

Проектування

схем

виділення фронтів часового інтервалу

Для формування сигналів початку часового інтервалу служать формувачі імпульсів (детектори фронтів). Детектор фронтів призначений для формування коротких імпульсів у момент перемикання логічних перепадів.

До складу детектора фронтів входить детектор заднього і переднього фронту. Так як необхідно вимірювати тривалість імпульсу, то детектор переднього фронту підключається до S-входу тригера, а детектор заднього фронту до R-входу.

Виберемо

тригер на основі МС КР1533ТР2 (чотири

RS-тригера). Основний режим - режим

зберігання, при цьому на входах

і

і

високий рівень напруги. При подачі

низького рівня на один з входів, на

виході встановлюється високий/низький

рівні напруги.

високий рівень напруги. При подачі

низького рівня на один з входів, на

виході встановлюється високий/низький

рівні напруги.

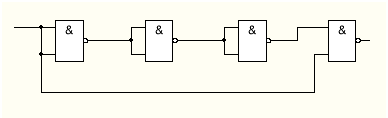

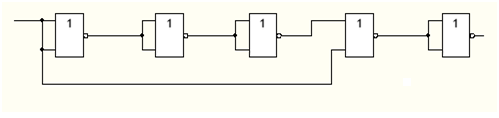

Для реалізації детектора переднього фронту виберемо елементи І-НЕ на основі мікросхеми К1533ЛА3. 4 елемента І-НЕ сформують імпульс необхідний для спрацювання тригера.

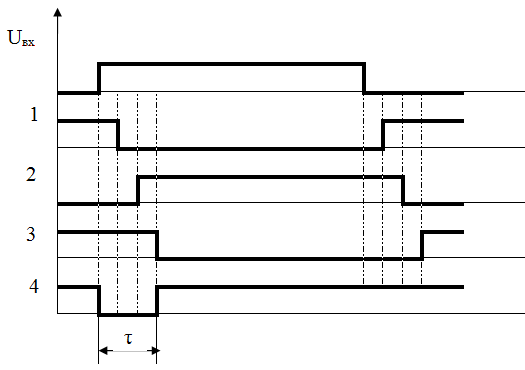

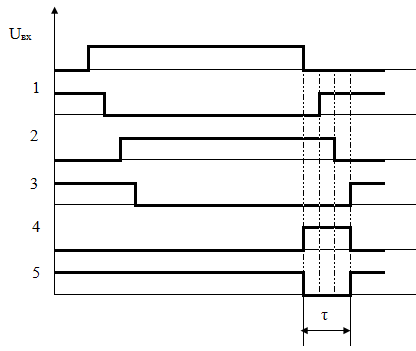

Рисунок 6 – Схема ДПФ

Рисунок 7 – Часова діаграма ДПФ

Для реалізації детектора заднього фронту виберемо елементи АБО-НЕ на основі мікросхеми К1533ЛЕ1. 4 елементи АБО-НЕ сформують імпульс необхідний для спрацювання тригера, а так як тригер керується нулями, для створення імпульсу низького рівня скористаємося п'ятим елементом АБО-НЕ.

Рисунок 8 – Схема ДЗФ

Рисунок 9 – Часова діаграма ДЗФ

Рисунок 10 – Схема детектора фронтів

3.3

Проектування

генератора

3.3

Проектування

генератора

Генератор тактових імпульсів забезпечує роботу лічильника і перетворювача паралельного коду в послідовний. Для забезпечення необхідної частоти для двох пристроїв використовуємо подільники частоти з заданим коефіцієнтом перерахунку.

Для

побудови генератора тактових імпульсів

необхідно розрахувати його частоту,

ґрунтуючись на точності вимірювання і

швидкості передачі. Знайдемо найменше

спільне кратне і отримаємо

.

.

Знайдемо коефіцієнти перерахунку для подільника частоти:

- для лічильника:

-

для перетворювача кода:

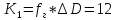

Найпростіший автогенератор можна побудувати на логічних елементах І-НЕ (АБО-НЕ або інверторах), в якому зворотний зв'язок через конденсатор охоплює два елементи DD1.10 і DD1.11, при чому DD1.10 виведений у лінійний підсилювальний режим за допомогою резистора негативного зворотного зв'язку R1=220 Ом. Елемент DD1.12 застосовується щоб зменшити вплив навантаження на частоту автогенератора.

Рисунок 11 – Схема тактового генератора

Частота

автогенерації

Частота

автогенерації

.

.

Тому:

.

.

В якості інверторів виберемо мікросхему КР1533ЛА3.

Побудуємо подільники частоти з заданими коефіцієнтами перерахунку.

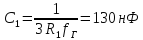

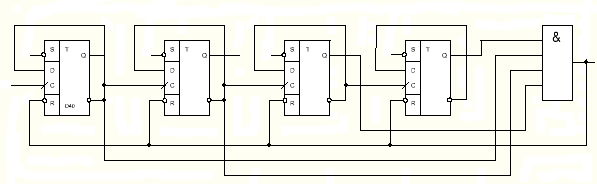

Рисунок 12 – Подільник частоти з коефіцієнтом перерахунку рівним 12

Рисунок 13 – Подільник частоти з коефіцієнтом перерахунку рівним 5

3.4

Проектування розрахункового

пристрою

3.4

Проектування розрахункового

пристрою

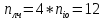

В якості лічильника для підрахунку тактових сигналів використовуємо двійково-десятковий лічильник з кодом 5121. Для побудови лічильника використовуємо JK-тригери. Синтезуємо сумуючий лічильник на основі JK-тригерів.

Таблиця 1 - Таблиця істинності розрахункової декади

|

№ |

Q1 |

Q2 |

Q3 |

Q4 |

Десят. цифра |

Q1 |

Q2 |

Q3 |

Q4 |

P |

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

J4 |

K4 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

* |

0 |

* |

0 |

* |

1 |

* |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

* |

0 |

* |

1 |

* |

* |

1 |

|

2 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

1 |

0 |

0 |

* |

0 |

* |

* |

0 |

1 |

* |

|

3 |

0 |

0 |

1 |

1 |

3 |

0 |

1 |

1 |

1 |

0 |

0 |

* |

1 |

* |

* |

0 |

* |

0 |

|

4 |

0 |

1 |

0 |

0 |

* |

* |

* |

* |

* |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

|

5 |

0 |

1 |

0 |

1 |

* |

* |

* |

* |

* |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

|

6 |

0 |

1 |

1 |

0 |

* |

* |

* |

* |

* |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

|

7 |

0 |

1 |

1 |

1 |

4 |

1 |

0 |

0 |

0 |

0 |

1 |

* |

* |

1 |

* |

1 |

* |

1 |

|

8 |

1 |

0 |

0 |

0 |

5 |

1 |

0 |

0 |

1 |

0 |

* |

0 |

0 |

* |

0 |

* |

1 |

* |

|

9 |

1 |

0 |

0 |

1 |

6 |

1 |

0 |

1 |

0 |

0 |

* |

0 |

0 |

* |

1 |

* |

* |

1 |

|

10 |

1 |

0 |

1 |

0 |

7 |

1 |

0 |

1 |

1 |

0 |

* |

0 |

0 |

* |

* |

0 |

1 |

* |

|

11 |

1 |

0 |

1 |

1 |

8 |

1 |

1 |

1 |

1 |

0 |

* |

0 |

1 |

* |

* |

0 |

* |

0 |

|

12 |

1 |

1 |

0 |

0 |

* |

* |

* |

* |

* |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

|

13 |

1 |

1 |

0 |

1 |

* |

* |

* |

* |

* |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

|

14 |

1 |

1 |

1 |

0 |

* |

* |

* |

* |

* |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

|

15 |

1 |

1 |

1 |

1 |

9 |

0 |

0 |

0 |

0 |

1 |

* |

1 |

* |

1 |

* |

1 |

* |

1 |