Файл: Методические указания для проведения практических работ по профессиональному модулю Проектирование цифровых устройств.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 28.03.2024

Просмотров: 88

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

Практическая работа №25.

Тема: Исследование работы ОЗУ на ИМС.

Цель: Получить практические навыки монтажа и отладки схемы ОЗУ.

Теоретическая часть

Запоминающие устройства

Память - это такое устройство в мозгу

при помощи которого мы все забываем

А. Чейз

Цифровые запоминающие устройства (ЗУ), сокращенно называемые также памятью, служат для хранения информации и обмена ею с другими устройствами. Это, безусловно, одно из важнейших ЦУ, определяющих многие характеристики ПК. Для кратковременного хранения кодовых слов используют регистры, а для длительного хранения и для больших объемов информации служат специализированные микросхемы. Поскольку далее речь пойдет только о полупроводниковой памяти, то отметим, что микросхемы памяти занимают до 40% от общего выпуска микросхем.

Важнейшими характеристиками ЗУ являются их информационная емкость, организация и быстродействие.

Основным классификационным признаком ЗУ является способ доступа к данным (способ обращения к массиву элементов памяти), по которому они подразделяются на адресные, последовательные и ассоциативные.

Адресные ЗУ в свою очередь подразделяются на RAM (Random Access Memory - память с произвольным доступом) и ROM (Read-Only Memory - память только для чтения). В отечественной литературе эти типы ЗУ называются соответственно Оперативным Запоминающим Устройством (ОЗУ) и Постоянным Запоминающим Устройством (ПЗУ) Первые, как правило, энергозависимы, а вторые, напротив - энергонезависимы. Среди ОЗУ различают устройства статические - Static RAM (SRAM) и динамические - Dynamic RAM (DRAM).

Статические ПЗУ

В ЗУ с произвольным доступом для хранения каждого бита информации используется отдельный запоминающий элемент - ячейка памяти (ЯП). Обычно в этом качестве используются различного рода триггеры. Двоичная информация, занесенная в подобную ЯП, хранится там сколь угодно долго, пока не будет заменена другой или не будет отключено питание (энергозависимая память).

В зависимости от способа, которым находится каждая ЯП в массиве, различают структуры с одномерной (линейной) и двумерной адресацией.

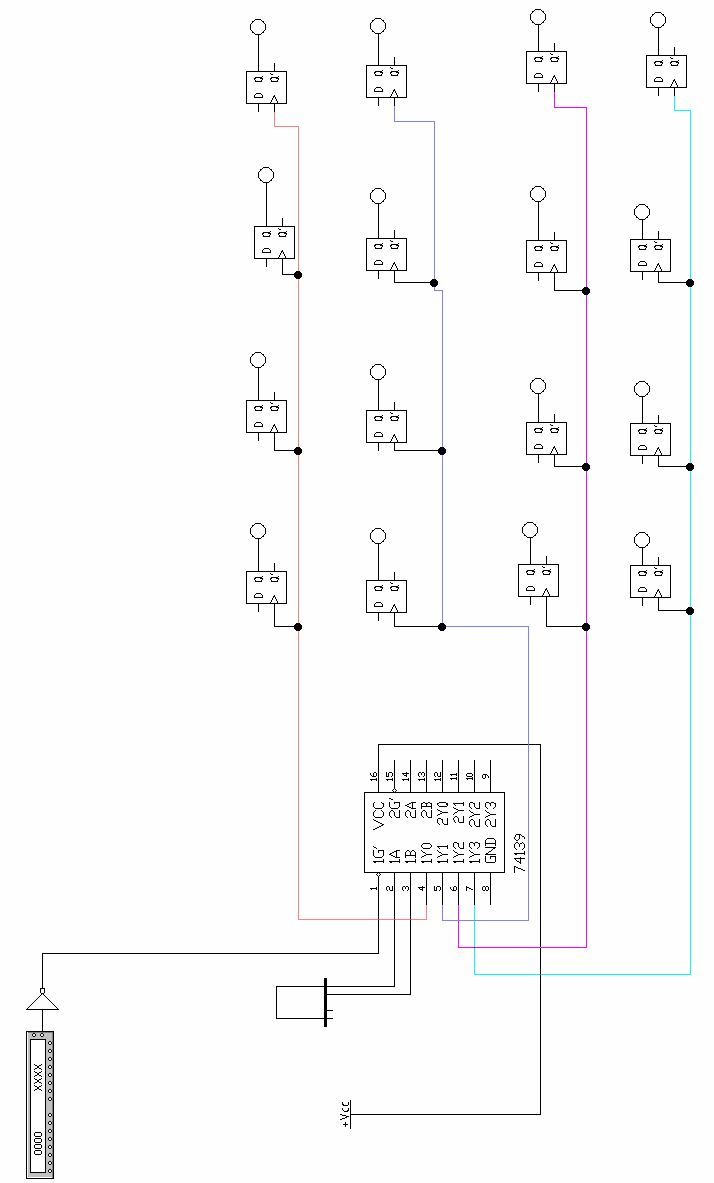

На рис. 1 в программе EWB представлена модель SRAM с линейной (пословной) адресацией. Здесь 16 ЯП из D-триггеров образуют квадратную матрицу 4x4. Через соответствующий вход D в ЯП вводится информация, по команде на входе С. Информация хранится на выходе Q или считывается с него по аналогичной команде. Адресация к ЯП производится ключами А и В, и далее декодером DC_2*4. Заносимые в конкретные ячейки биты информации набираются на генераторе слов. Тактовый сигнал с этого же генератора используется для синхронизации триггеров, декодера и мультиплексоров, а выход 5-го разряда - для формирования сигнала типа разрешение записи/чтения. Записи соответствует лог. О, а чтению - лог. 1. Вывод информации (чтение) производится по столбцам через мультиплексоры MUX4x1 Для наглядности работы модели она снабжена тремя дисплеями, которые (сверху вниз) отображают: вводимое слово, адрес ЯП и читаемое слово. Кроме того, в каждой ЯП поставлен индикатор ее состояния. Разумеется, это всего лишь иллюстративная, но работающая модель. На рис. 1 показано, что ключи А=В=0, т.е произведено считывание из верхнего ряда ЯП, занесенного туда ранее слова (1100)2=A16= 1010. В данной системе считанная информация исчезает из памяти: как бы нельзя два раза войти в одну и ту же реку.

Расшифровка элементов схемы

-

Индикаторы - нумерация ножек

-

D-триггер. Используются вход D, C1 , выход Q ( к нему подключается лампочка)

-

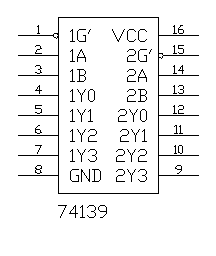

Д ешифратор (декодер)

ешифратор (декодер)

Выход 1А соединяется с первым выходом индикатора

Выход 1В соединяется с вторым выходом индикатора

Выход 1Y0 соединяется с выходами С1 первой линии триггеров.

Выход 1Y1 с выходами С1 второй линии триггеров.

Выход 1Y2 с выходами С1 третьей линии триггеров Выход 1Y1 с выходами С1 четвертой линии триггеров

Выход VCC подключается к питанию.

Выход 1G’ подключается через элемент НЕ к генератору слов.

4. Входы верхнего индикатора идут к генератору слов.

5. В качестве мультиплексора берется спаренная микросхема

Выходы 1G’и 2G’ подключаются к генератору слов.

Выходы 1С0, 1С1, 1С2, 1С3, 2С1, 2С2, 2С3 подключаются к выходам триггеров Q сверху вниз ( 1 и 2 столбцы) с учетом подключения лампочек.

Выходы 1Y, 2Y подключаются на входы D нижнего ряда триггеров.

Выход VCC – питание.

Выход GND – земля.

Выход В подключается ко второму выходу второго индикатора. Выходы А соединяются между собой.

Выходы нижнего индикатора соединяются с выходами D нижнего ряда триггеров 1 -1,

2 -2, 3 – 3, 4 – 4 (триггеры считать слева – направо.

Вход второго нижнего элемента НЕ идет к пятому входу генератора слов.

-

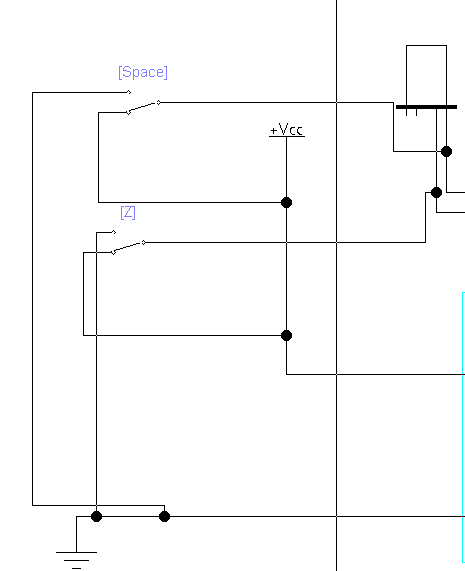

Ключи. Двойной щелчок по элементу – назначить клавишу для замыкания (размыкания)

Работа схемы

В окно генератора слов занести:

Поочередно замыкая ключи и нажимая кнопку Step сначала выделив строку 000А запускать схему 4 раза. Выбрав строку 0010 запустить схему еще раз.

СПИСОК ЛИТЕРАТУРЫ

Основные источники:

-

Кардашев Г.А. Цифровая электроника на персональном компьютере.Electronics Workbench и Micro-Cab- 2е изд., стереотип.- М.:Горячая линия- Телеком, 2014.-312с.: ил.-(Массовая радиобиблиотека;1263) -

Пухальский Г.И. Проектирование цифровых устройств+СD. Изд-во: СПб. «Лань»,2014г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Герасимов А.С. Курс математической логики и теории вычислимости. Изд-во: « Лань», 2014г.ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Попов В.Д. Физические основы проектирования кремниевых цифровых интегральных микросхем в монолитном и гибридном исполнении. Изд-во:«Лань»,2014г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Строгонов А.В. Цифровая обработка сигналов в базисе программируемых логических интегральных схем. Изд-во: « Лань», 2014г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Чулков В.А. Схемотехника ЭВМ. Учебник в 6ч. – Пенза: Изд-во Пенз. гос.тех. академии, 2014. -

(Электронный ресурс) Белоус А.И. Основы схемотехники микроэлектронных устройств. М.: Техносфера, 2014- 472с. -

(Электронный ресурс)Гаврилов с.А. Искусство схемотехники. Просто о сложном. СПб.:Наука и техника, 2014-352с. -

(Электронный ресурс) Лаврентьев Б.Ф. Схемотехника электронных средств. М.:Академия, 2014-336с. -

(Электронный ресурс) Глинкин Е.А. Схемотехника аналоговых интегральных схем: учебное пособие. Тамбов, 2014г.-152с. -

(Электронный ресурс) Шеин А.Б. Методы проектирования электронных устройств М.: Инфра – инженерия, 2014-456с. -

Журнал Компьютер Пресс -

Журнал CHIP -

Журнал Компоненты и технологии

Дополнительные источники:

-

И. М. Мышляева Цифровая схемотехника. Учебник для сред. Проф. образования – М.: Издательский центр «Академия», 2014. – 400с. -

Браммер Ю.А. Импульсные и цифровые устройства. – М., 2014. -

Келим Ю.М. Вычислительная техника: учебное пособие для СПО. – М.: Академия, 206. -

Алексеев Е.Б. Проектирование и техническая эксплуатация цифровых телекоммуникационных систем и сетей. Издательство Горячая линия-Телеком. Изд-во: СПб. « Лань», 2014г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Герман- Галкин С.Г. Виртуальные лаборатории полупроводниковых систем в среде Matlab-Simulink. Изд-во: « Лань», 2015г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Глухов М.М. Математическая логика. Дискретные функции. Теория алгоритмов. Изд-во: « Лань», 2015г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Трэвис Дж. LabVIEW для всех. Изд.: ДМКПресс , 2015г. ЭБС «Издательства Лань» http://e.lanbook.com/view/book/ -

Мелехин В.Ф., Павловский Е.Г. Вычислительные машины, системы и сети: учебник. – М.: Академия, 2014. -

Попов И.И., Партыка Т.Л. Вычислительная техника: учебное пособие. – М., 2014. -

Кузин А.В. Микропроцессорная техника: учебник для студентов СПО. – М., 2014. -

Норенков И.П. Основы автоматизированного проектирования: учебник для вузов. – М., 2014. -

Ольхов М. Основы проектирования сборочных единиц ЭВМ. - М., 2014. -

Бабич Н.П., Жуков И.А. Компьютерная схемотехника. – Киев: МК-Пресс, 2014. -

Бойко В.И. и др. Схемотехника электронных систем. Цифровые устройства. – СПб.: BHV–Санкт -Петербург, 2014. -

Грушвицкий Р.К. Проектирование систем на микросхемах программируемой логики. – СПб.: BHV–Санкт-Петербург, 2014. -

Каган Б.М. Электронные вычислительные машины и системы: учеб. пос. для вузов. – М., 2014. -

Калабеков Б.А. Цифровые устройства и микропроцессорные системы.- М., 2014. -

Нарышкин А.К. Цифровые устройства и микропроцессоры: учеб. пос. для вузов. – М., 2014. -

Угрюмов Е. Цифровая схемотехника. – СПб., 2014. -

Хоровиц П. Искусство схемотехники. – М., 2014. -

Микропроцессоры и микроконтроллёры. – СПб., 2014. -

Журнал «CHIP C DVD/ ЧИП С DV» 2012г.-№№ 1-12,2013г. -№№ 1-12, 2014г. -№№ 1-12, 2015г.-№№ 1-12 -

Журнал «КомпьютерПресс» 2012г.-№№ 1-12,2013г. -№№ 1-12, 2014г .-№№ 1-6 -

Журнал «Компоненты и технологии» 2016г.-№№1-12, 2017г.-№№1-6

Интернет-ресурсы, учебно-методические пособия.

-

http://www.intuit.ru - Интернет-университет информационных технологий (ИНТУИТ.ру) -

http://www.iteach.ru - Программа Intel «Обучение для будущего» -

http://www.rusedu.info - Сайт RusEdu: информационные технологии в образовании -

http://www.osp.ru - Открытые системы: издания по информационным технологиям -

http://www.labirint.ru/ - Магазин книг -

edu - "Российское образование" Федеральный портал -

edu.ru - ресурсы портала для общего образования -

fepo - "Федеральный Интернет-экзамен в сфере профессионального образования" -

allbest - "Союз образовательных сайтов" -

ed.gov - "Федеральное агентство по образованию РФ". -

obrnadzor.gov - "Федеральная служба по надзору в сфере образования и науки" -

mon.gov - Официальный сайт Министерства образования и науки Российской Федерации -

rost.ru/projects - Национальный проект "Образование". -

window.edu.ru - Единое окно доступа к образовательным ресурсам -

Портал "ВСЕОБУЧ" -

rgsu.net - Российский Государственный Социальный Университет.