Файл: Методические указания для проведения практических работ по профессиональному модулю Проектирование цифровых устройств.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 28.03.2024

Просмотров: 138

Скачиваний: 0

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

мультиплексора подаются двоичные данные, то его также называют селектором данных. Операция переключения из множества линий данных на одну носит название мультиплексирования.

Задание 1.

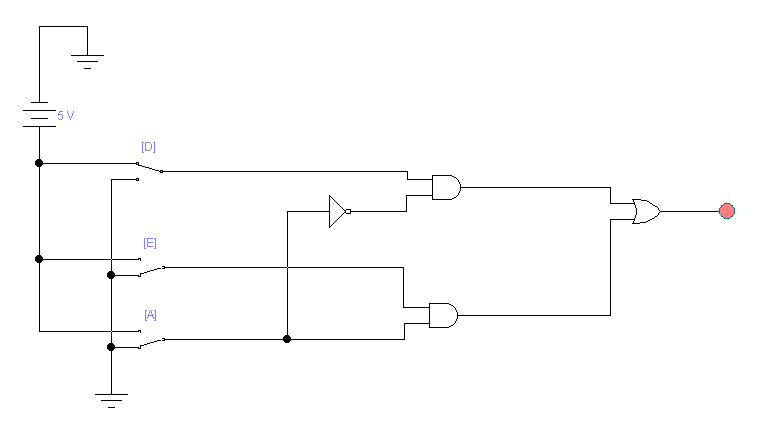

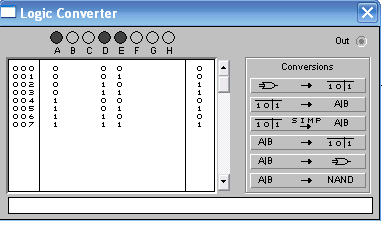

Собрать схему мультиплексора и проверить ее работу.

Скопировать фрагмент схемы в новый файл и проверить таблицу истинности работы данной функции

Задание 2.

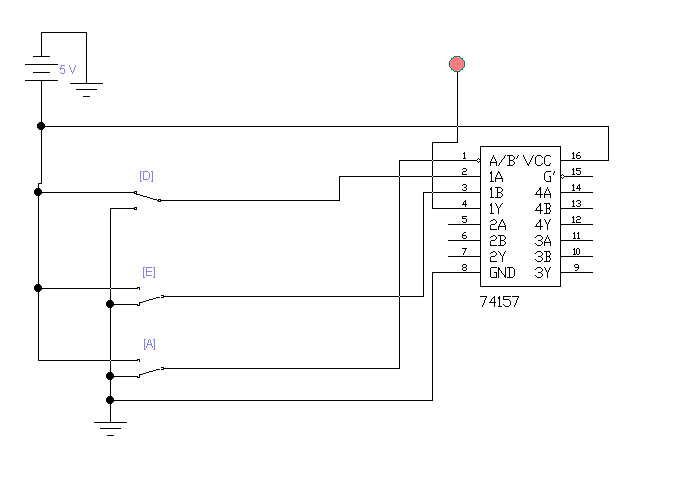

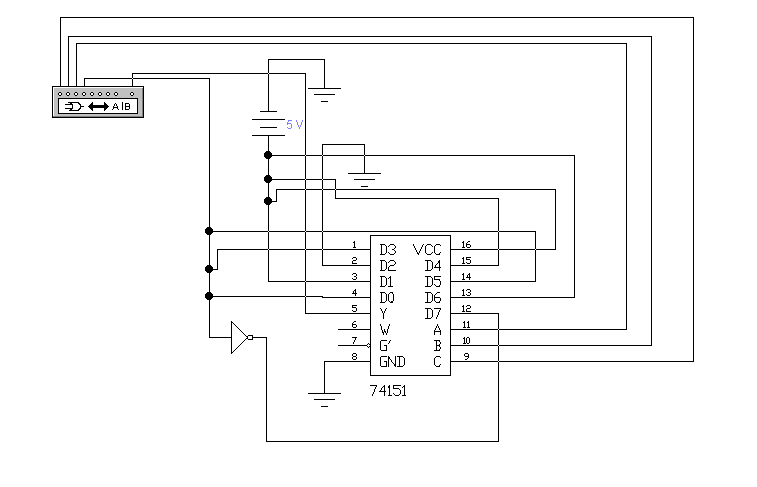

Собрать схему мультиплексора на основе микросхемы и проверить ее работу.

Задание 3.

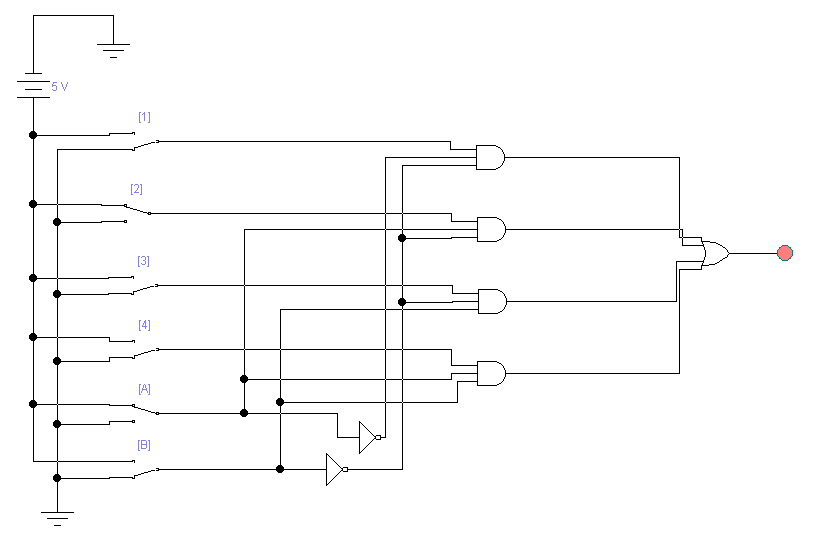

Собрать схему мультиплексора 4х1 и проверить ее работу.

Задание 4.

Собрать схему мультиплексора 4х1 на основе микросхемы и проверить ее работу.

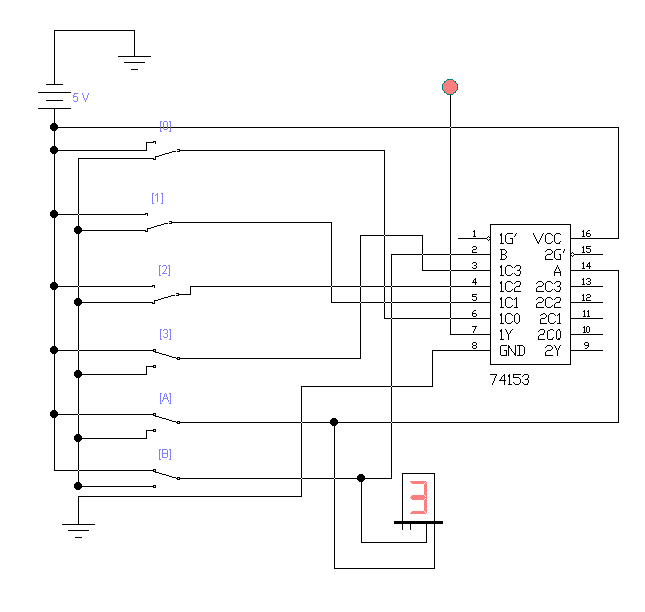

Используя стандартную микросхему ТТЛ 74153, содержащую в корпусе два мультиплексора 4х1, можно продемонстрировать ее работу. На адресных входах набрано в двоичном коде число 3 и сигнал с входного канала 3, равный 1, попадает на выход - выходной индикатор горит.

Задание 5.

Синтезировать схему для реализации логический функции (n+1)-го аргумента на мультиплексоре с n адресными входами за счет переноса одного из аргументов в число информационных сигналов. Дана функция.

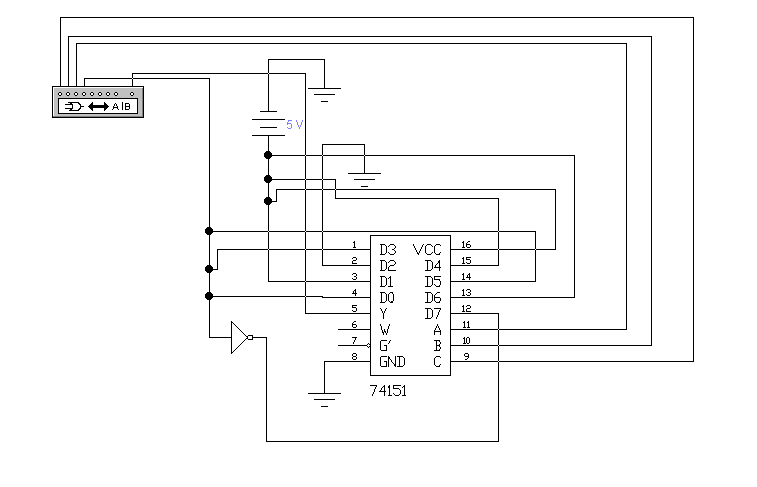

Тема: Исследование работы демультиплексора на ИМС.

Цель: Получить практические навыки исследования работы демультиплексора.

Теоретическая часть

Задание 1.

Собрать схему демультиплексора и проверить ее работу по таблице истинности

Задание 2.

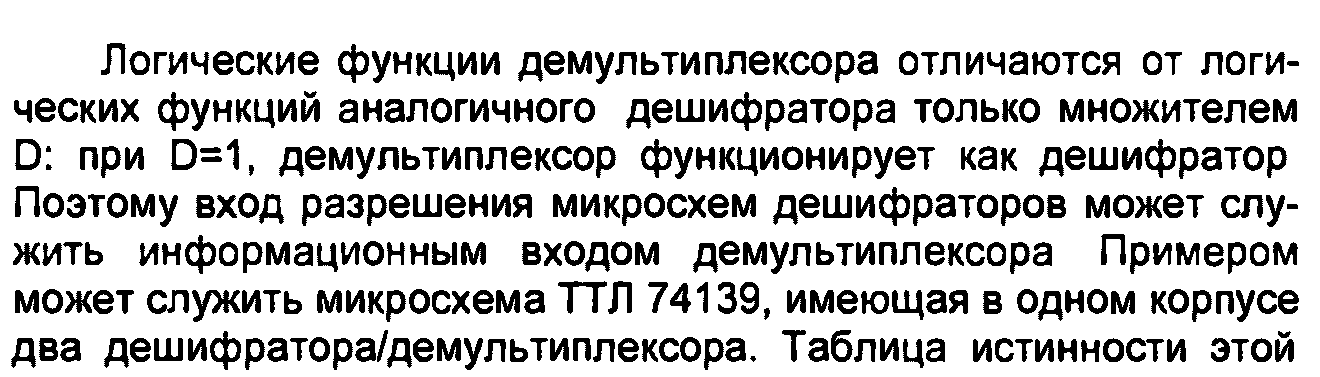

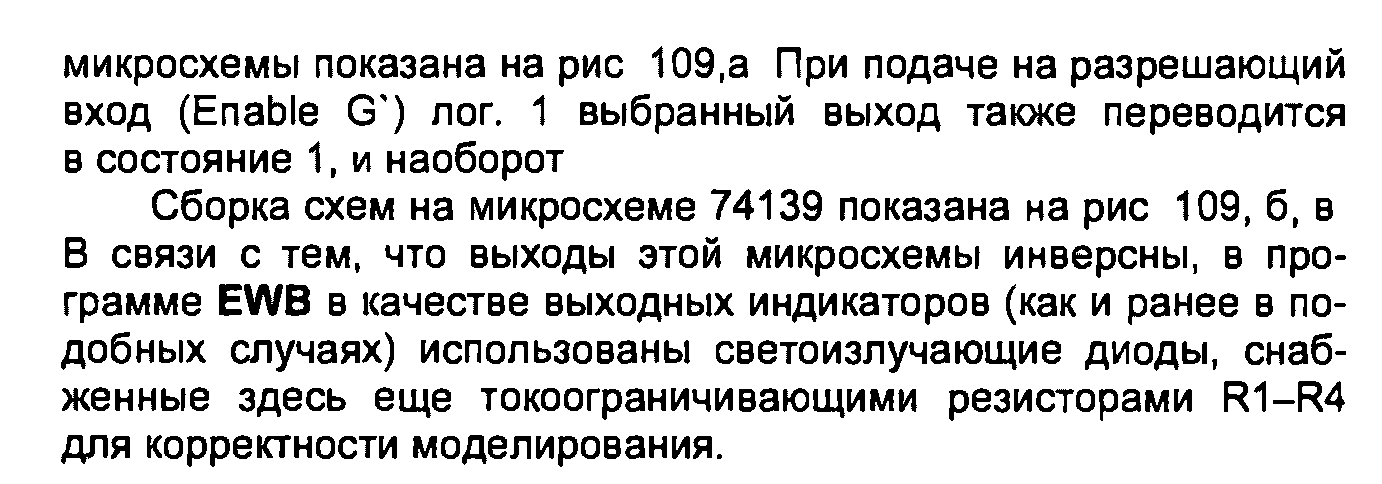

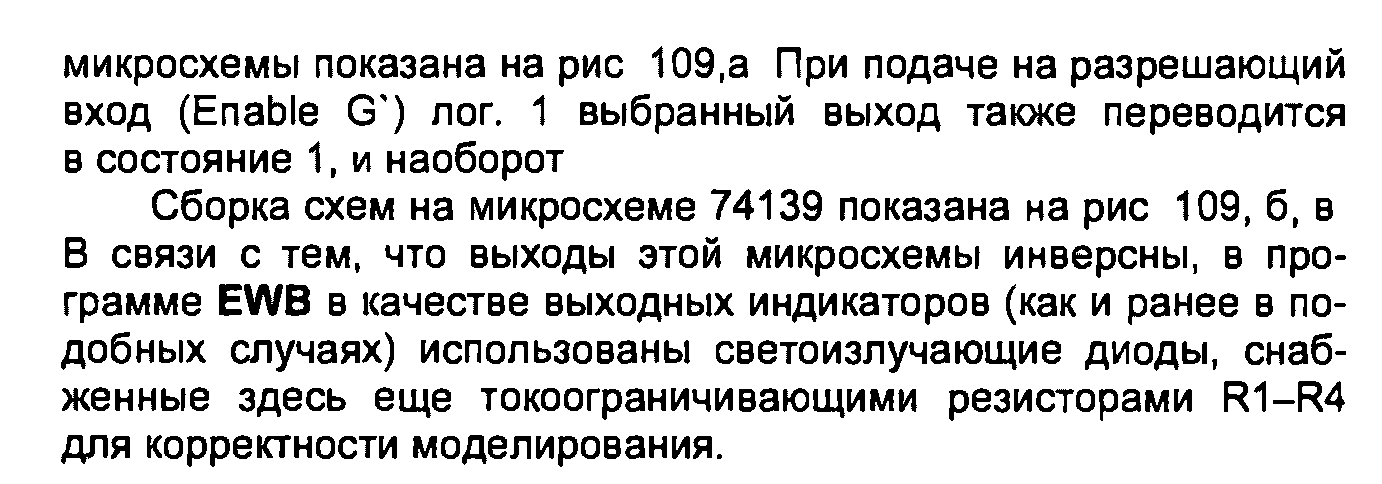

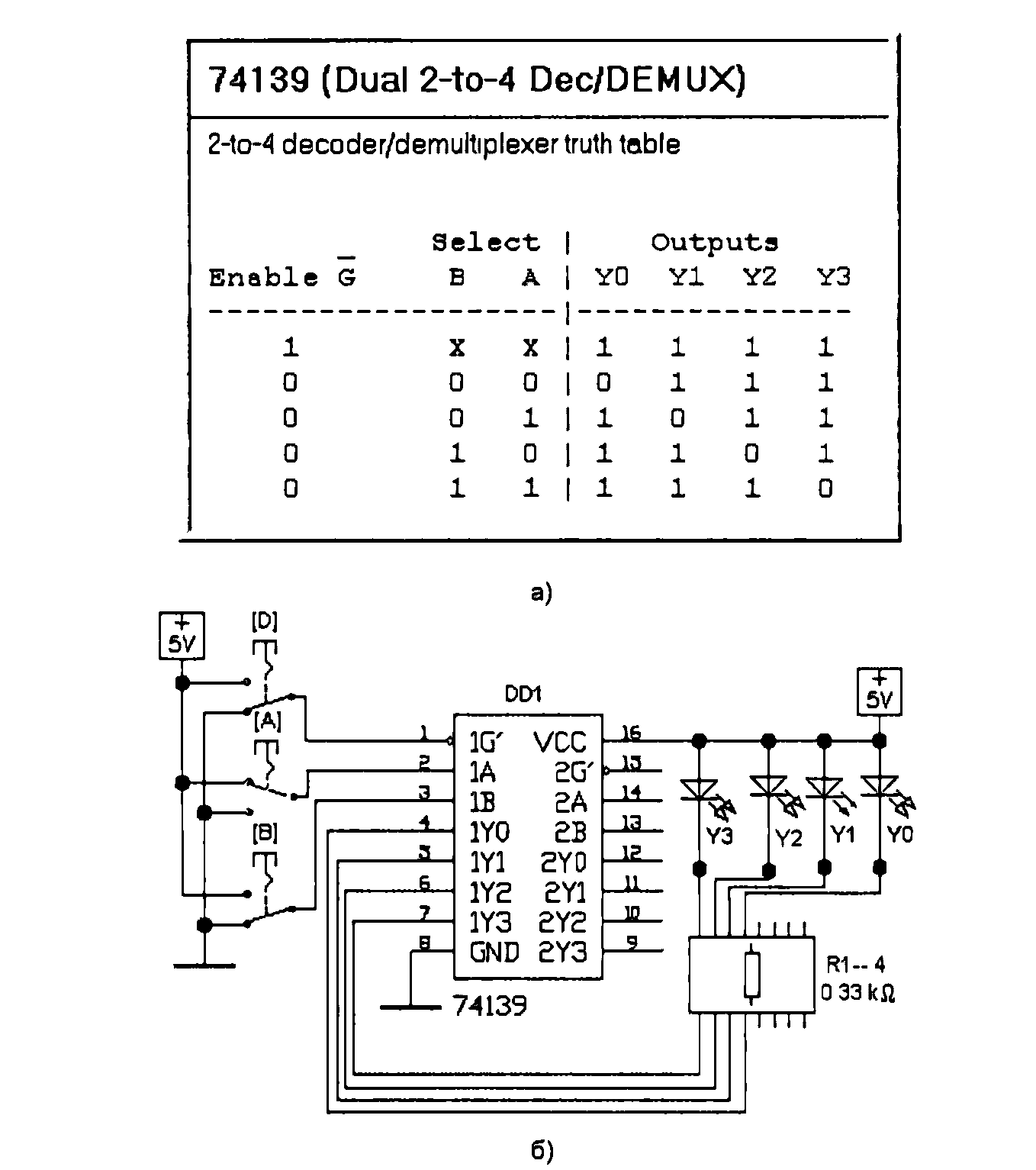

Собрать схему демультиплексора на базе микросхемы и проверить ее работу по таблице истинности

Тема: Исследование работы компаратора на ИМС.

Цель: Получить практические навыки исследования работы компараторов.

Изучение назначения устройства и принцип работы цифрового компаратора.

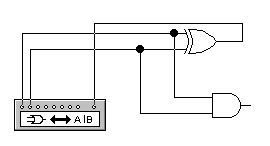

Цифровые компараторы (от английского compare – сравнивать) выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А=В или неравенства АB. Результат сравнения отображается в виде логического сигнала на одноименных выходах, в случае выполнения условия на выходе 1.

Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для выполнения условных переходах.

Задание 1.

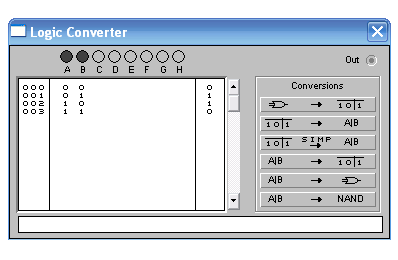

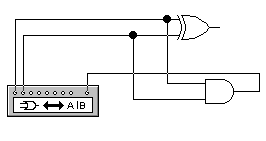

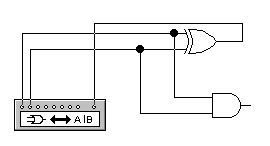

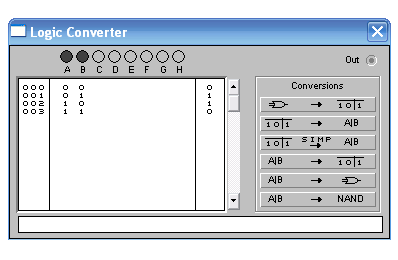

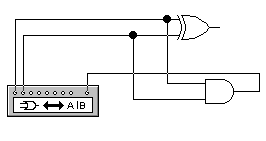

Схема A

Схема A>B (A B’)

B’)

Схема А=В (A’ B’+AB)

B’+AB)

Задание 2.

Построить схемы операций >=, <=, <> и проверить таблицы истинности.

Логические функции этих компараторов выглядят:

(A'·B)', (A·B')', (A'·B'+A·B)'.

Можем упростить данные формулы с помощью законов алгебры логики:

(A'·B)'=A''+B'=(закон де Моргана)=A+B' (закон двойного отрицания),

(A·B')'=A'+B''=A'+B,

(A'·B'+A·B)'=(A''+B'')·(A'+B')=(A+B)·(A'+B').

Тема Исследование работы двоичного сумматора на ИМС.

Цель работы: изучение принципов построения и специфики применения комбинационных сумматоров в типовых арифметических узлах.

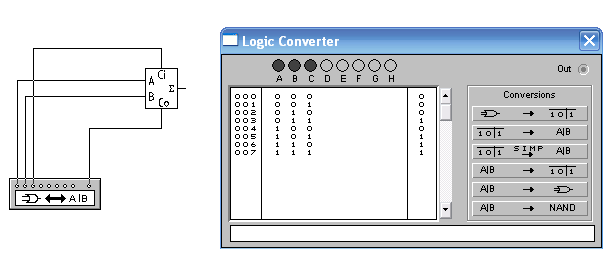

Задание 1. Исследование сумматоров:

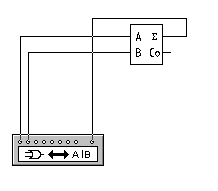

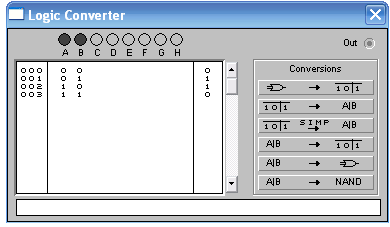

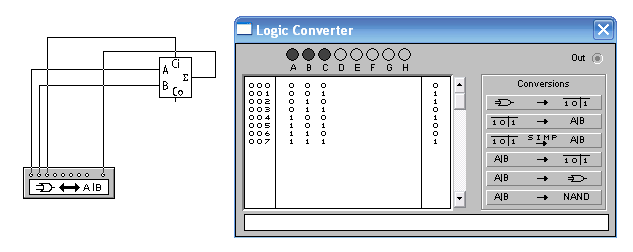

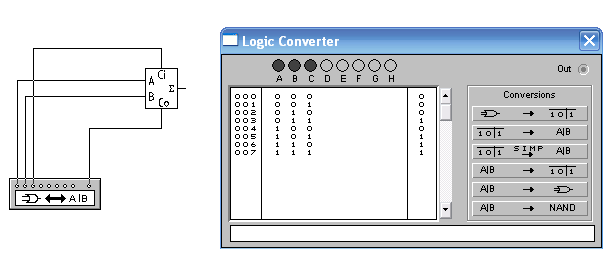

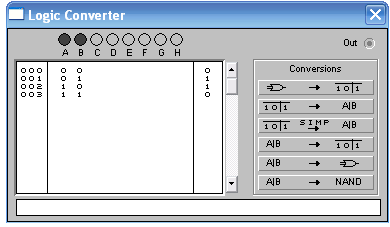

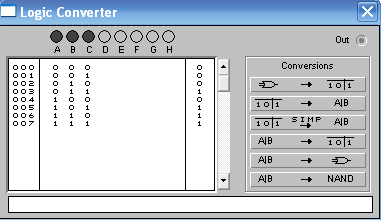

1. Построить схему полусумматора и проверить таблицу истинности.

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода C

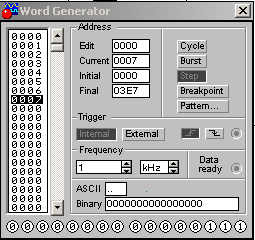

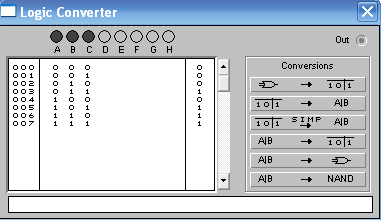

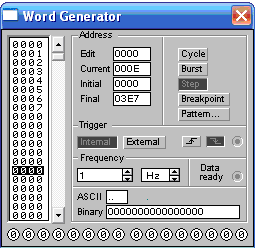

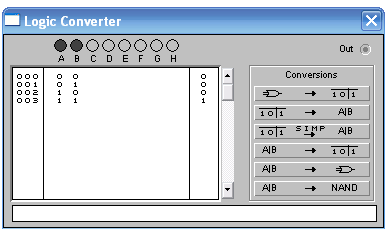

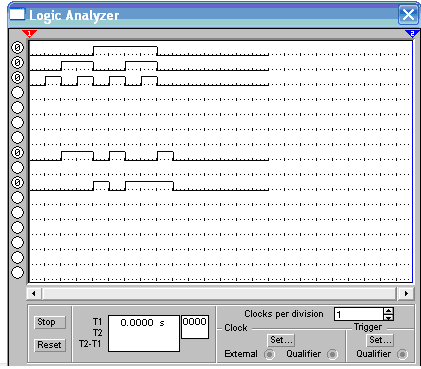

2.1. В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,2,3,4,5,6,7.

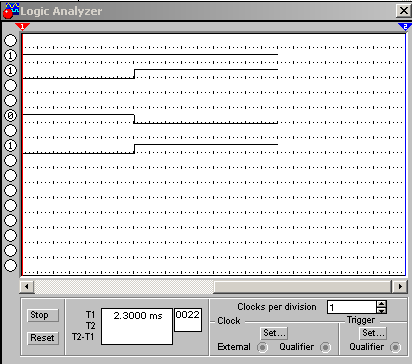

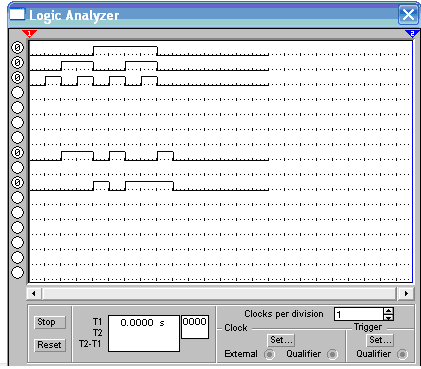

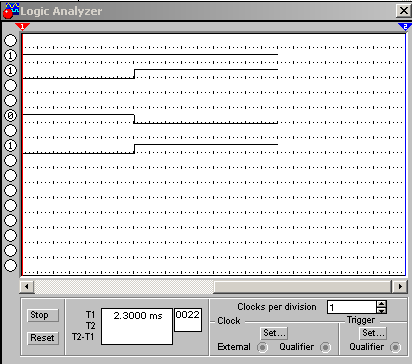

2 .2. Развернуть графический анализатор.

.2. Развернуть графический анализатор.

2.3. Запустить генератор слов в пошаговом режиме, кнопка Step и проследить как будет меняться окно графического анализатора.

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода С

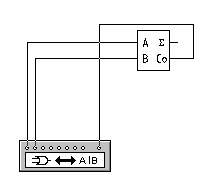

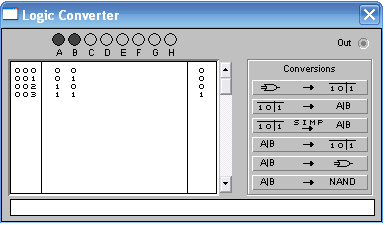

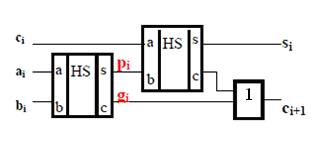

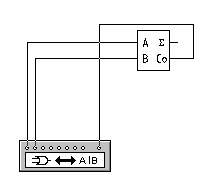

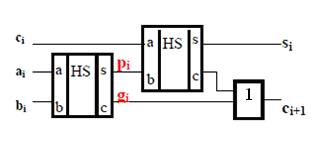

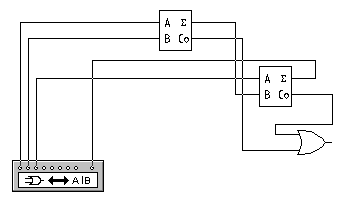

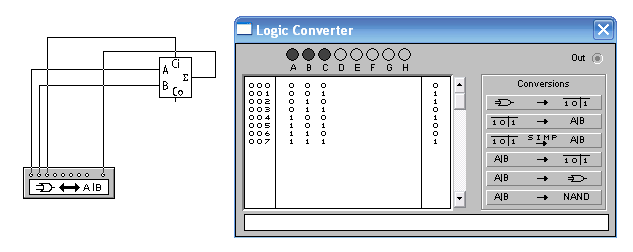

4. Построить схему полного сумматора и проверить таблицу истинности.

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода С

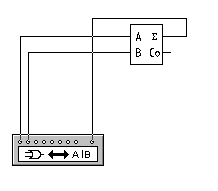

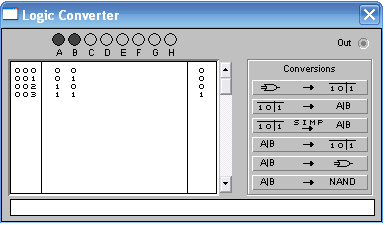

5. извлечь из магазина компонентов полный одноразрядный сумматор и проверить его функционирование на соответствие таблице истинности

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода С

6. Собрать схему полусумматора на логических элементах И-ИЛИ-НЕ

6.1. В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,2,3,4,5,6,7.

6.2. Развернуть графический анализатор.

6.3. Запустить генератор слов в пошаговом режиме, кнопка Step и проследить как будет меняться окно графического анализатора.

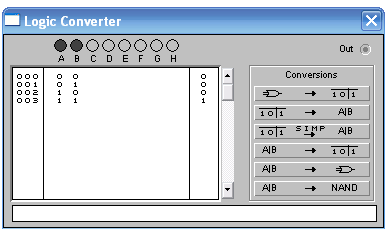

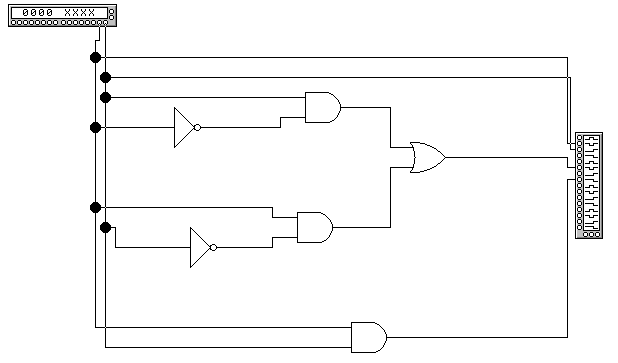

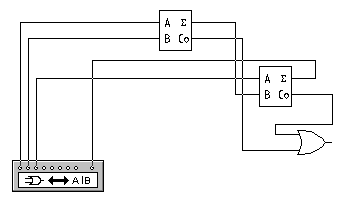

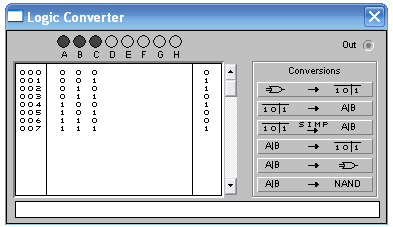

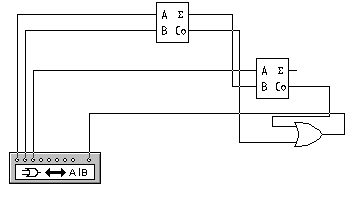

Задание 2

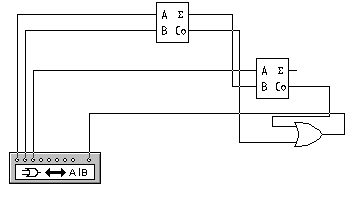

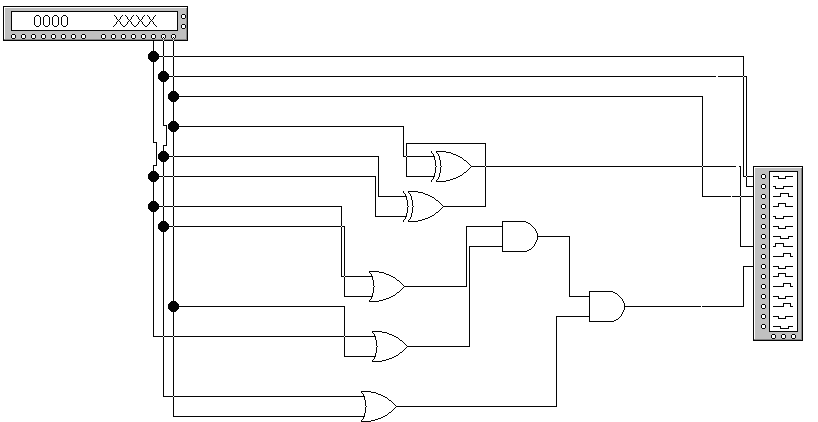

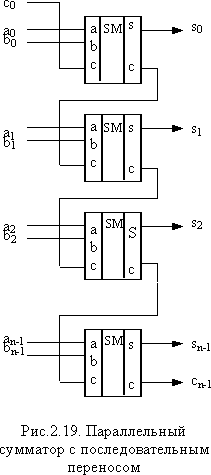

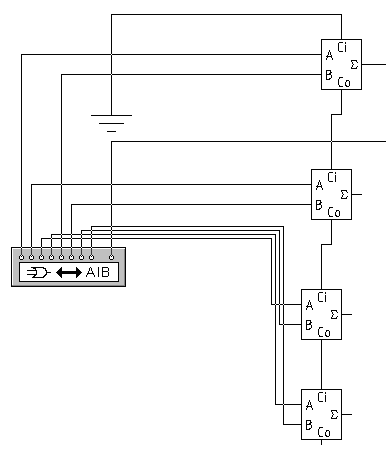

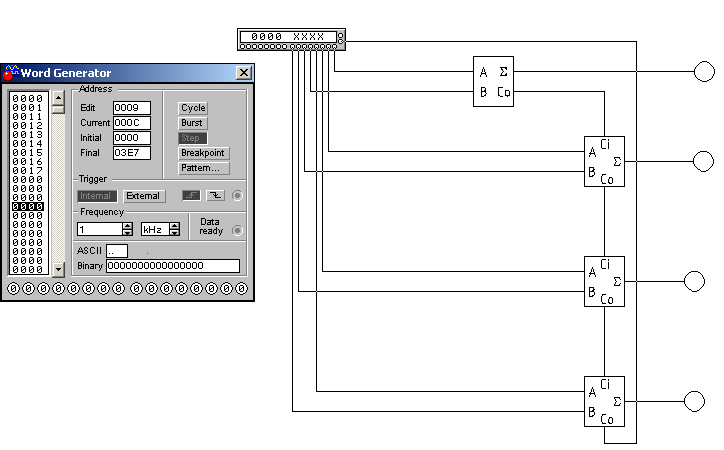

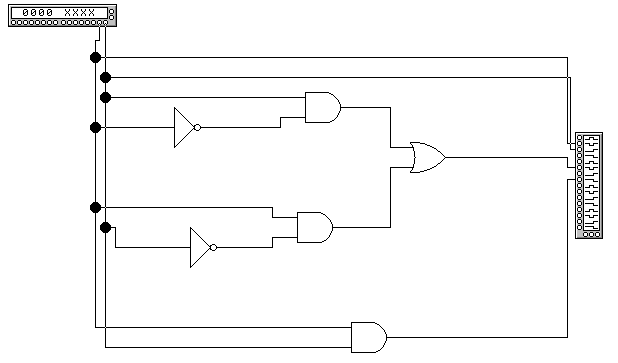

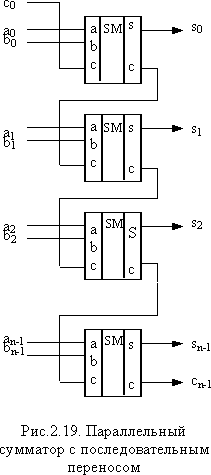

С обрать на основе полных одноразрядных сумматоров 4-разрядный параллельный сумматор с последовательным переносом и проверить его работу, задавая на входы А и В и вход переноса различные двоичные числа. Для формирования двоичных чисел можно использовать в качестве логического 0 шину земли, а в качестве логической 1 источник напряжения 5В из раздела Passive магазина компонентов;

обрать на основе полных одноразрядных сумматоров 4-разрядный параллельный сумматор с последовательным переносом и проверить его работу, задавая на входы А и В и вход переноса различные двоичные числа. Для формирования двоичных чисел можно использовать в качестве логического 0 шину земли, а в качестве логической 1 источник напряжения 5В из раздела Passive магазина компонентов;

Записать таблицу истинности для четырех выходов S и выхода переноса С

Исследовать четырехразрядный сумматор с помощью генератора слов.

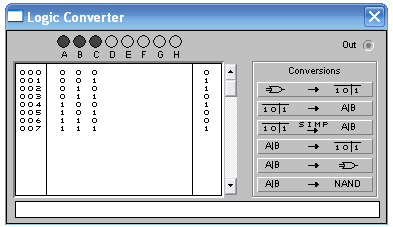

10. Собрать цифровую схему сравнения.

10.1. В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,2,3,4,5,6,7.

10.2. Развернуть графический анализатор.

10 .3. Запустить генератор слов в пошаговом режиме, кнопка Step и проследить как будет меняться окно графического анализатора.

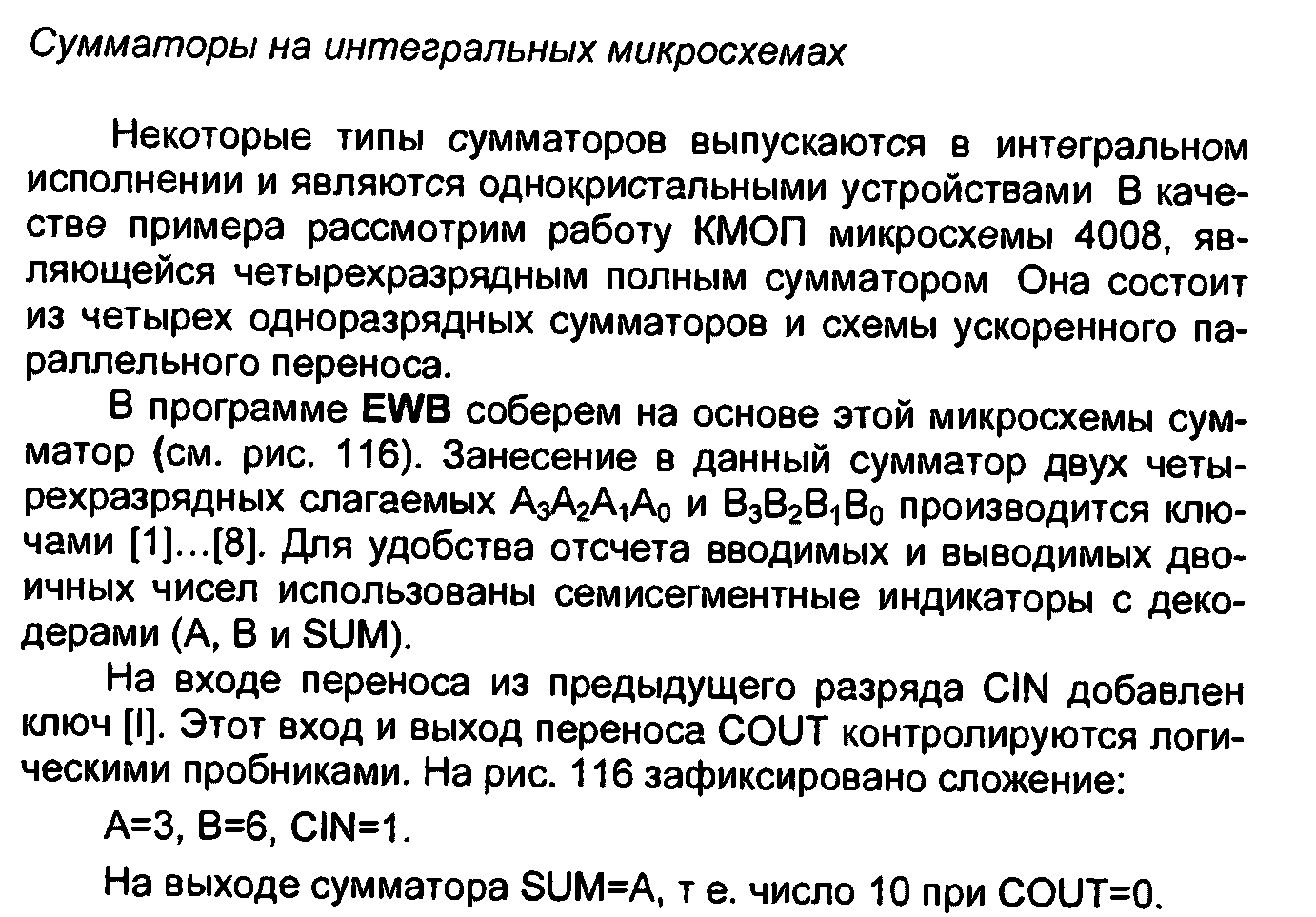

Задание 3.

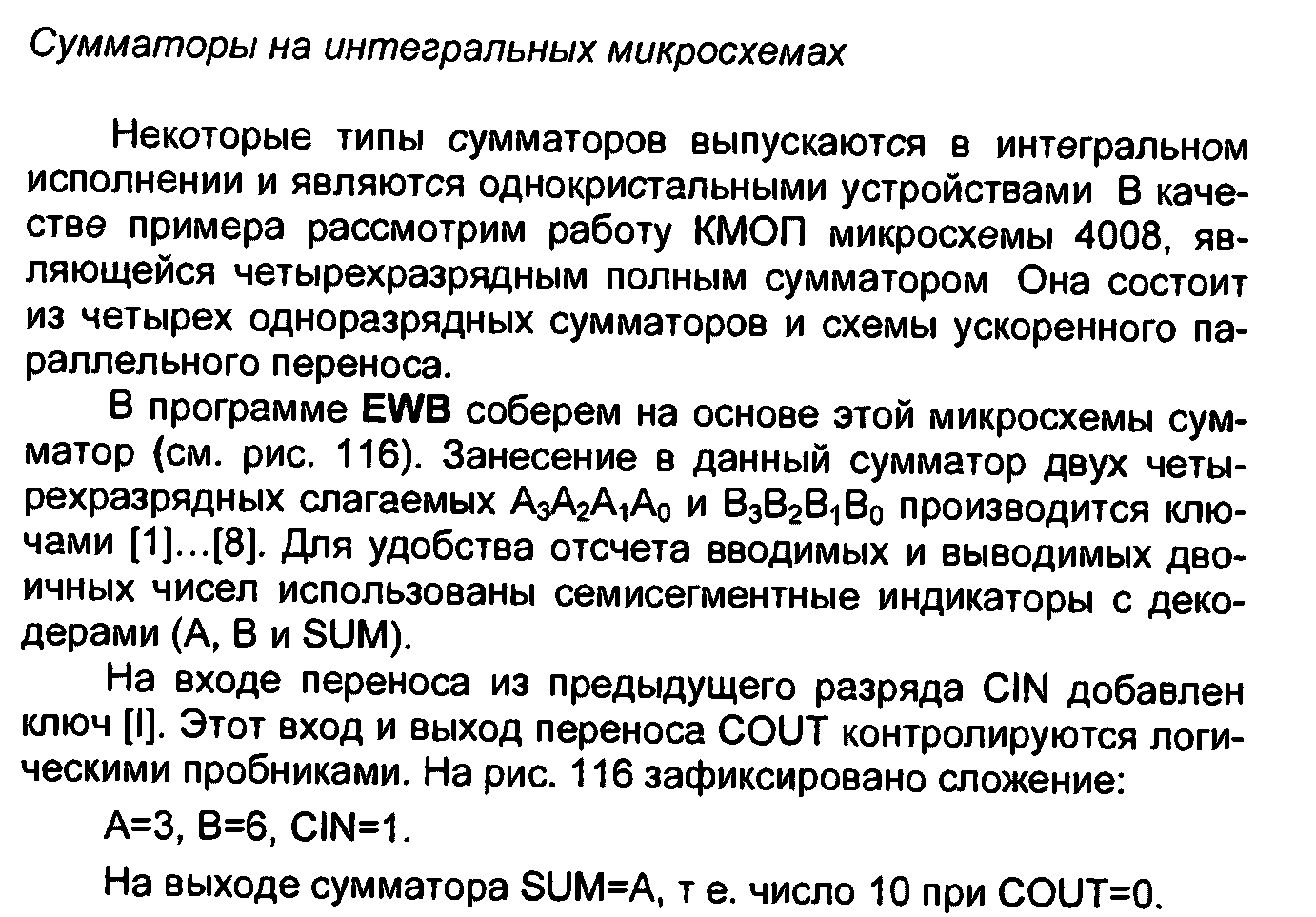

Собрать схему на базе микросхемы и проверить ее работу.

Практическая работа №20

Тема: Исследование работы АЛУ на ИМС.

Цель работы

Изучение функциональных возможностей, области применения и приобретение навыков работы с арифметико-логическими устройствами (АЛУ) на примере микросхемы К155ИП3.

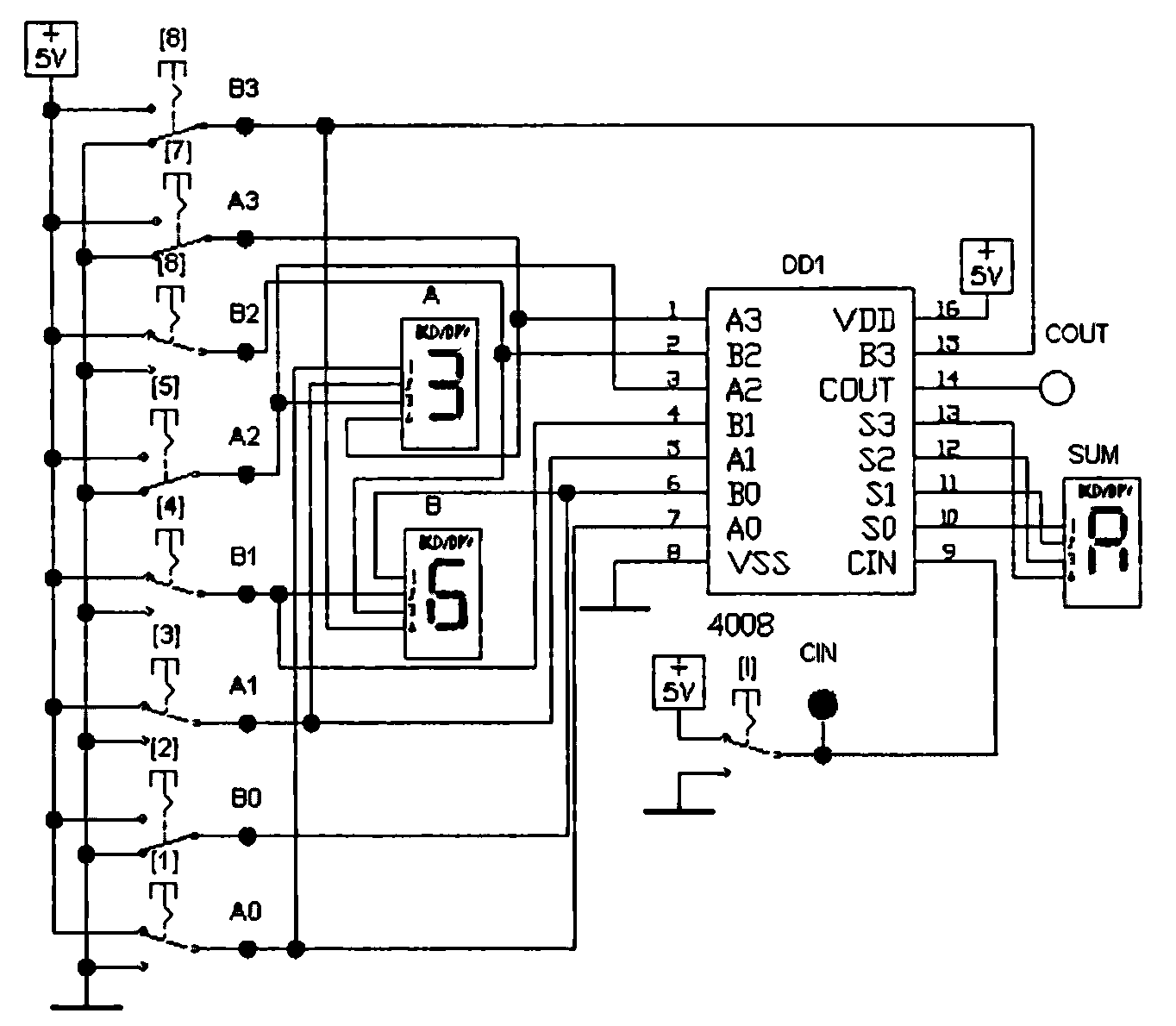

Задание 1.

Построить схему сложения двух чисел А и В.

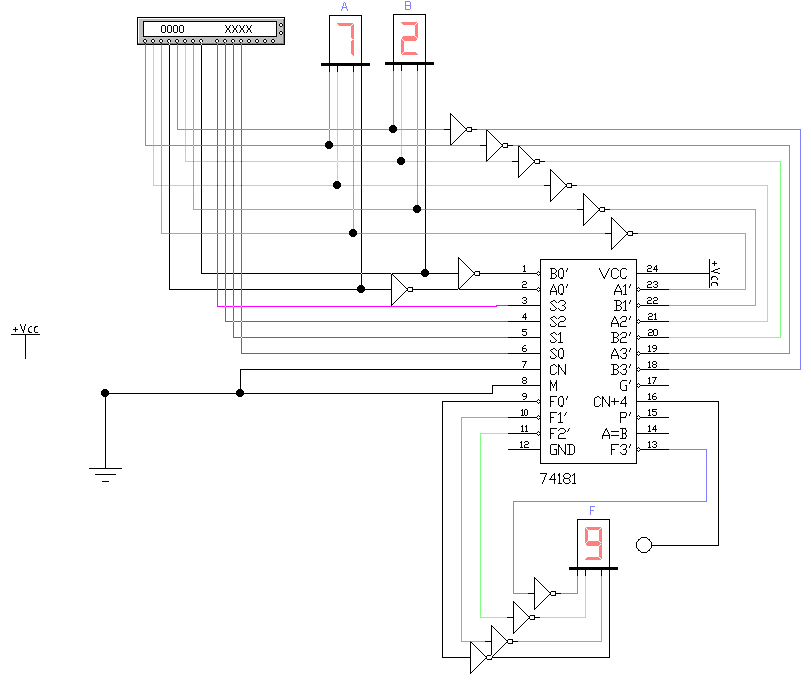

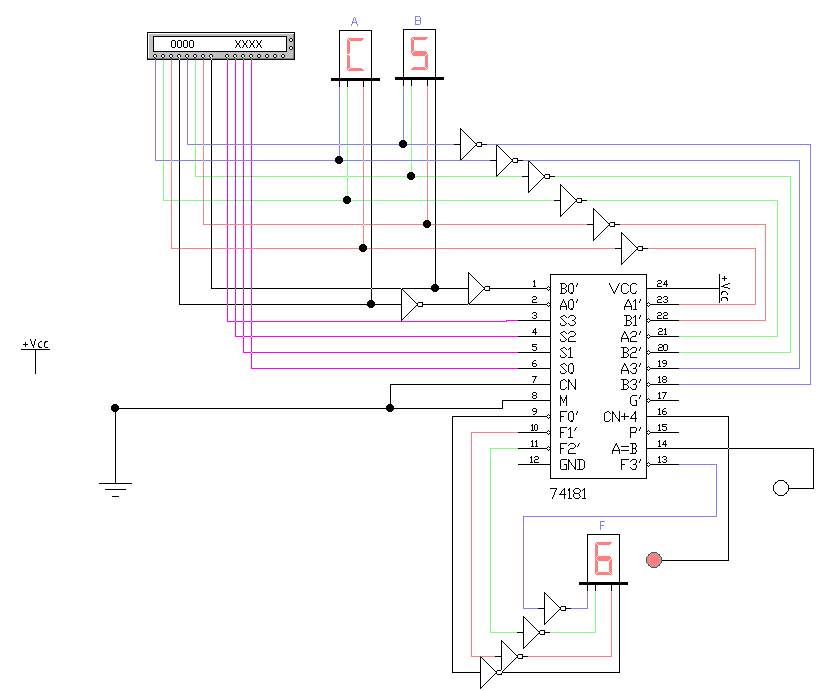

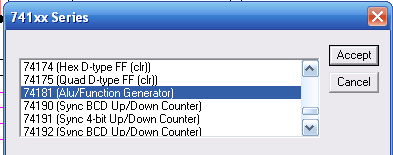

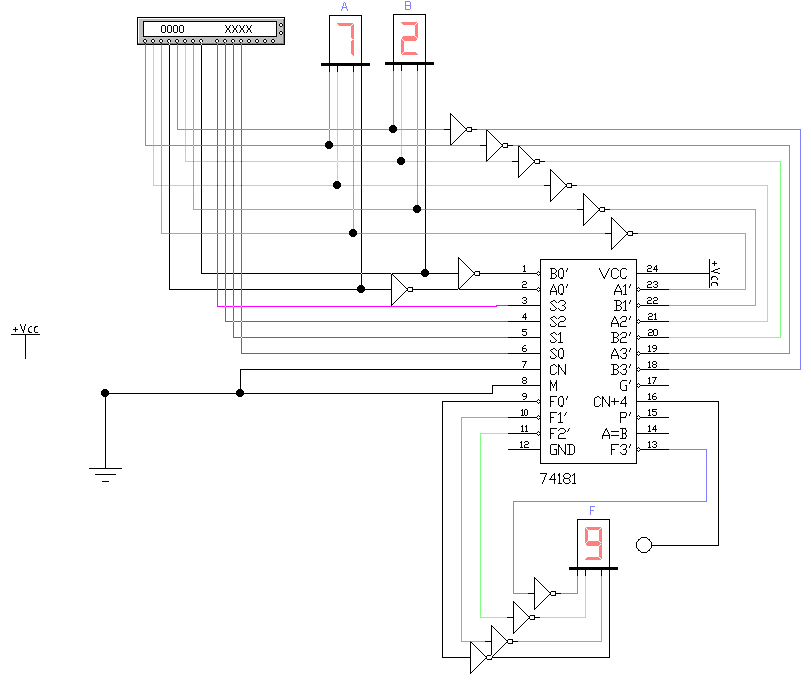

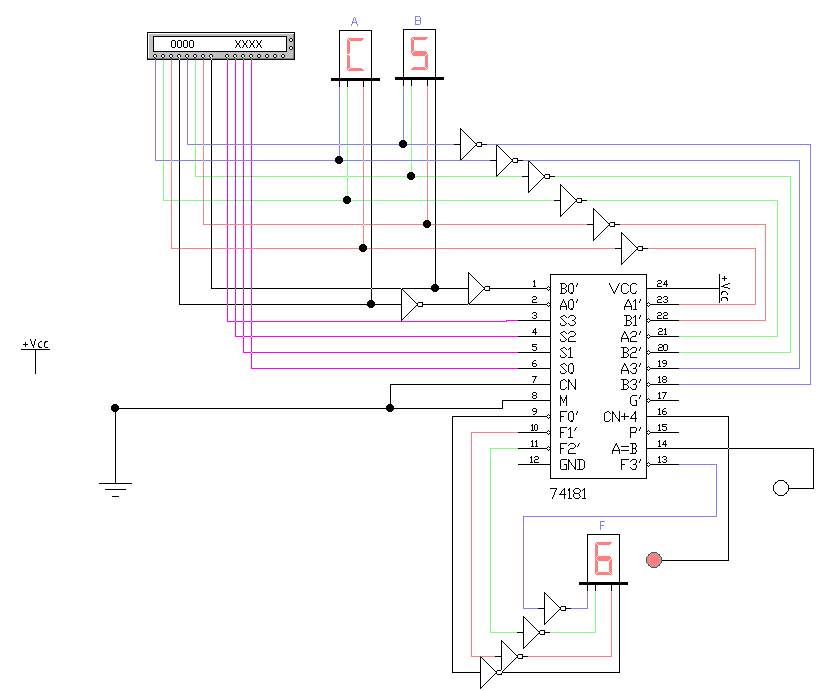

С оберем схему на основе микросхемы К155ИП3. В программе Electronics Workbench это микросхема из группы74181

оберем схему на основе микросхемы К155ИП3. В программе Electronics Workbench это микросхема из группы74181

Так как входы А0, А1, А2, А3 и В0, В1, В2, В3 инверсны, то перед ними ставим элементы НЕ. Входы М и СN заземляем, так кА работаем по отрицательной логике.

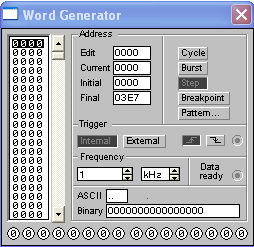

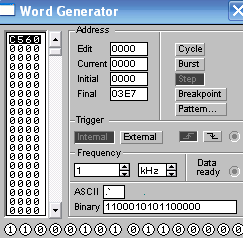

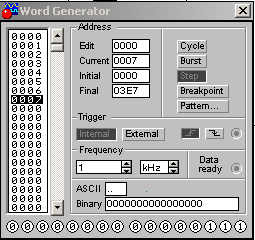

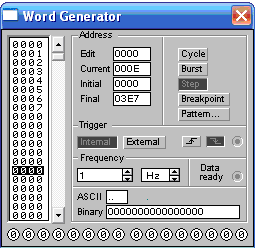

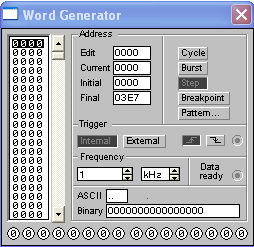

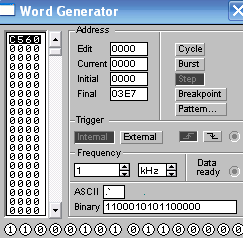

Откроем окно генератора слов.

A3 – A0 B3 – B0 S3 – S0

.

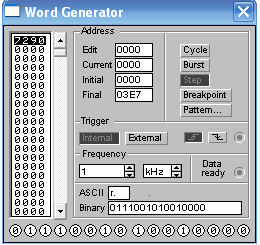

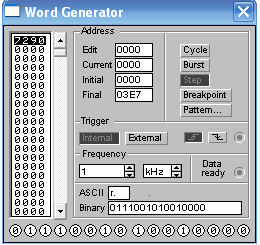

Для арифметического сложения, А плюс В на вход А подадим 7(0111) на вход В 2 (0010) на входы S 9(1001) согласно таблице. На выходе получим результат 9 и 0 в переносе.

Задание: Проверить все арифметические и логические операции таблицы работы АЛУ и отразить в своих примерах.

Пример проверить арифметическую операцию А плюс ( ) при А=516, В=С16

) при А=516, В=С16

- Логическое сложение, плюс арифметическое сложение

- Логическое сложение, плюс арифметическое сложение

В окне генератора слов введем: 5С40 (числа А и В и код операции 4). Т. К. операция арифметическая, М=0 и L=0.

С16

+ 0101

+ 0101

0011

0111

А плюс ( )= + 0101

)= + 0101

0111

1100

Задание 2.

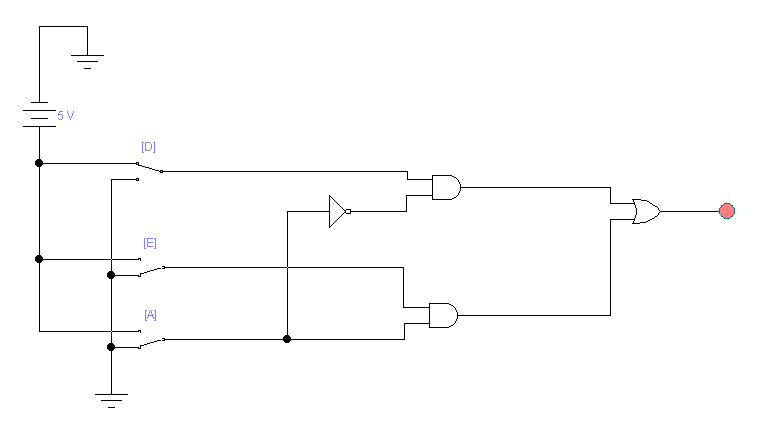

Проверить работу АЛУ в режиме компаратора. Для этого к выходу А=В (14) подключим индикатор.

По таблице (отрицательная логика) Проверим А>B. Выход CN=0. Подав на генератор слов комбинацию С560, проверим А=В (0), СN=1

З адание: Проверить работe АЛУ в режиме компаратора и отразить в своих примерах.

адание: Проверить работe АЛУ в режиме компаратора и отразить в своих примерах.

Тема: Синтез триггерной схемы

Цель: получить практические навыки создания и демонстрации работы триггерной схемы.

Задание

Спроектируйте синхронный триггер с информационными входами А и В, работающий в соответствии с заданной таблицей переключений, в двух вариантах: 1 - на основе JK-триггера; 2 - на основе D-триггера. В табл. 1 указаны состояния триггера до (Qn) и после (Qn+1) поступления синхросигнала.

Задание 1.

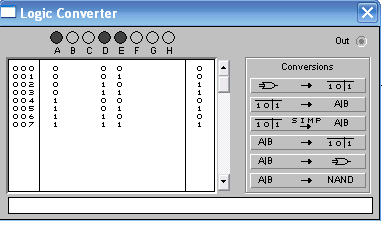

Собрать схему мультиплексора и проверить ее работу.

Скопировать фрагмент схемы в новый файл и проверить таблицу истинности работы данной функции

Задание 2.

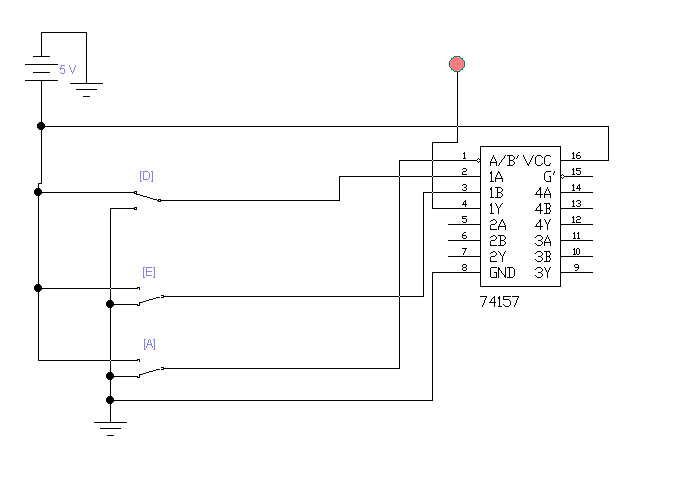

Собрать схему мультиплексора на основе микросхемы и проверить ее работу.

Задание 3.

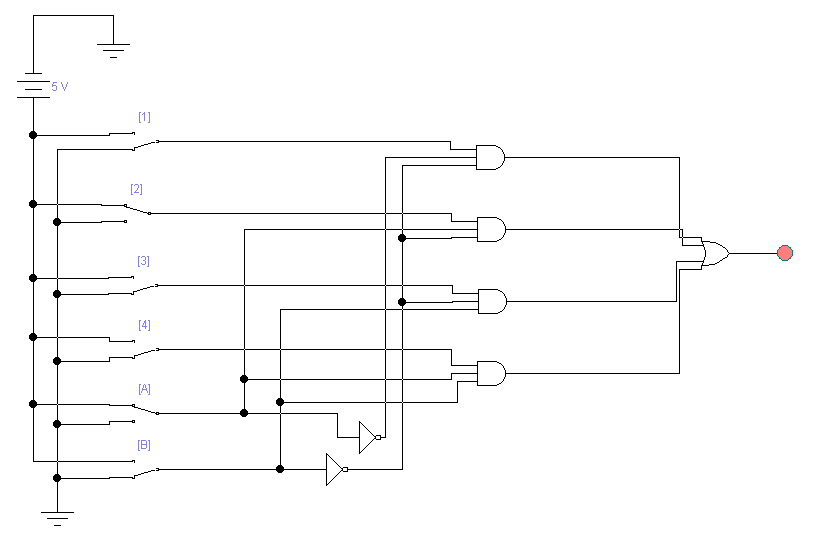

Собрать схему мультиплексора 4х1 и проверить ее работу.

Задание 4.

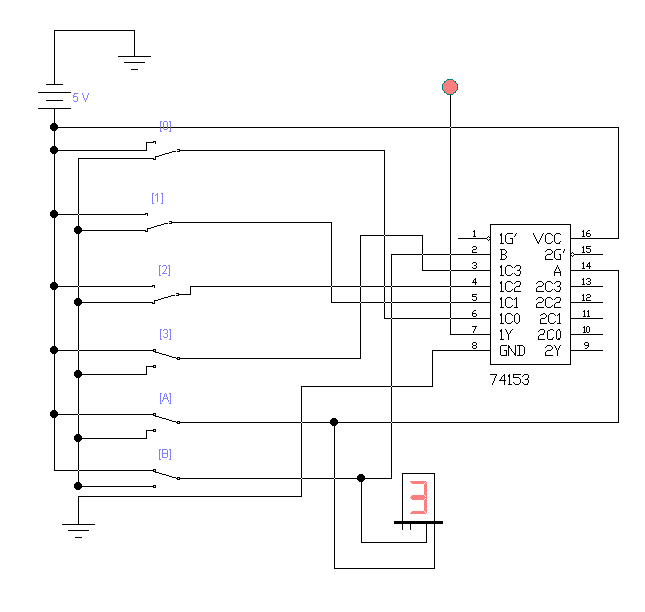

Собрать схему мультиплексора 4х1 на основе микросхемы и проверить ее работу.

Используя стандартную микросхему ТТЛ 74153, содержащую в корпусе два мультиплексора 4х1, можно продемонстрировать ее работу. На адресных входах набрано в двоичном коде число 3 и сигнал с входного канала 3, равный 1, попадает на выход - выходной индикатор горит.

Задание 5.

Синтезировать схему для реализации логический функции (n+1)-го аргумента на мультиплексоре с n адресными входами за счет переноса одного из аргументов в число информационных сигналов. Дана функция.

| x3 | х2 | х1 | х0 | F | F(x0) |

| 0 | 0 | 0 | 0 | 0 | F= x0 |

| 0 | 0 | 0 | 1 | 1 | |

| 0 | 0 | 1 | 0 | 1 | F=1 |

| 0 | 0 | 1 | 1 | 1 | |

| 0 | 1 | 0 | 0 | 0 | F=0 |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 0 | F= x0 |

| 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 1 | F= 1 |

| 1 | 0 | 0 | 1 | 1 | |

| 1 | 0 | 1 | 0 | 0 | F= x0 |

| 1 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 1 | F=1 |

| 1 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 |  |

| 1 | 1 | 1 | 1 | 0 |

Практическая работа №17.

Тема: Исследование работы демультиплексора на ИМС.

Цель: Получить практические навыки исследования работы демультиплексора.

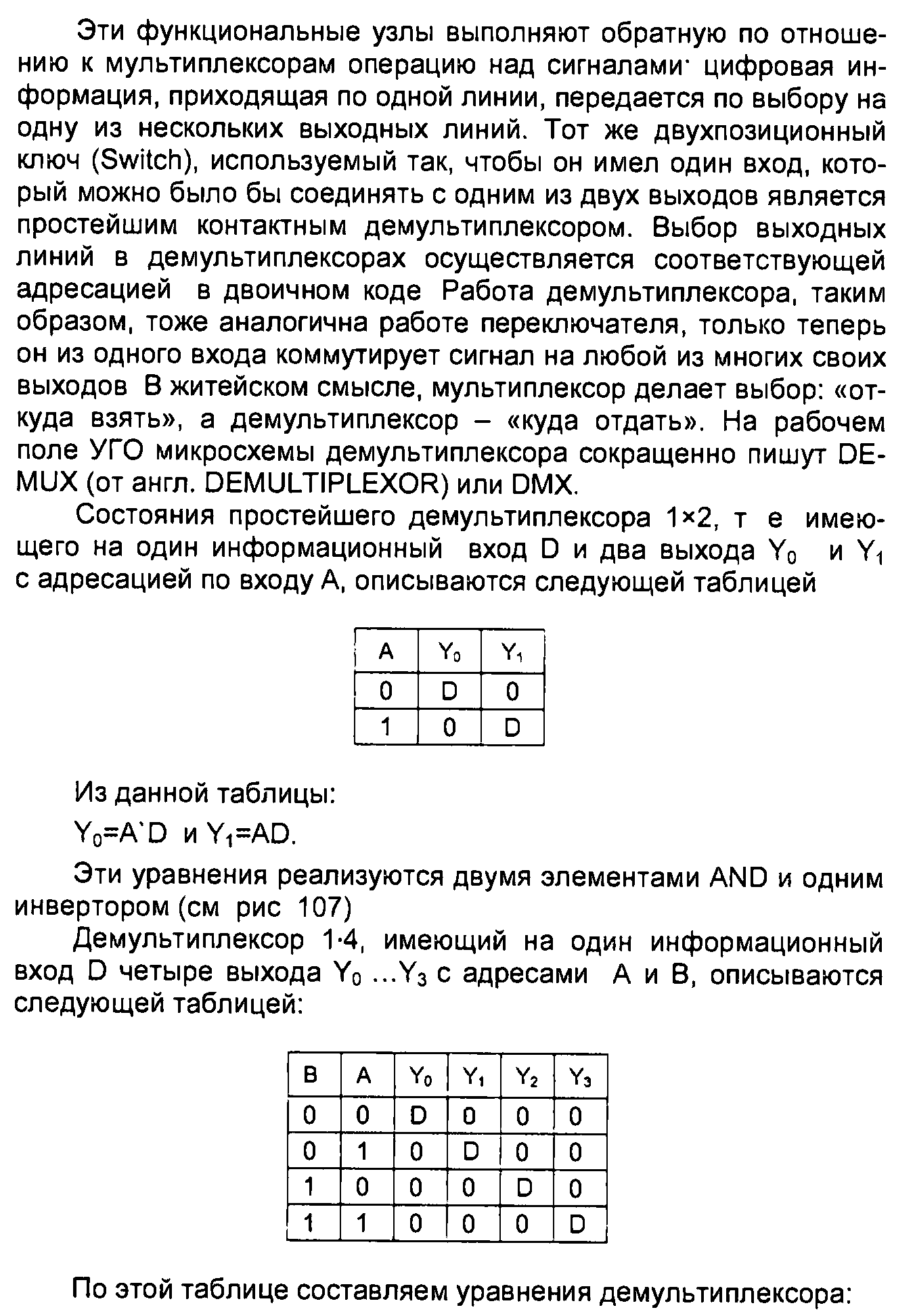

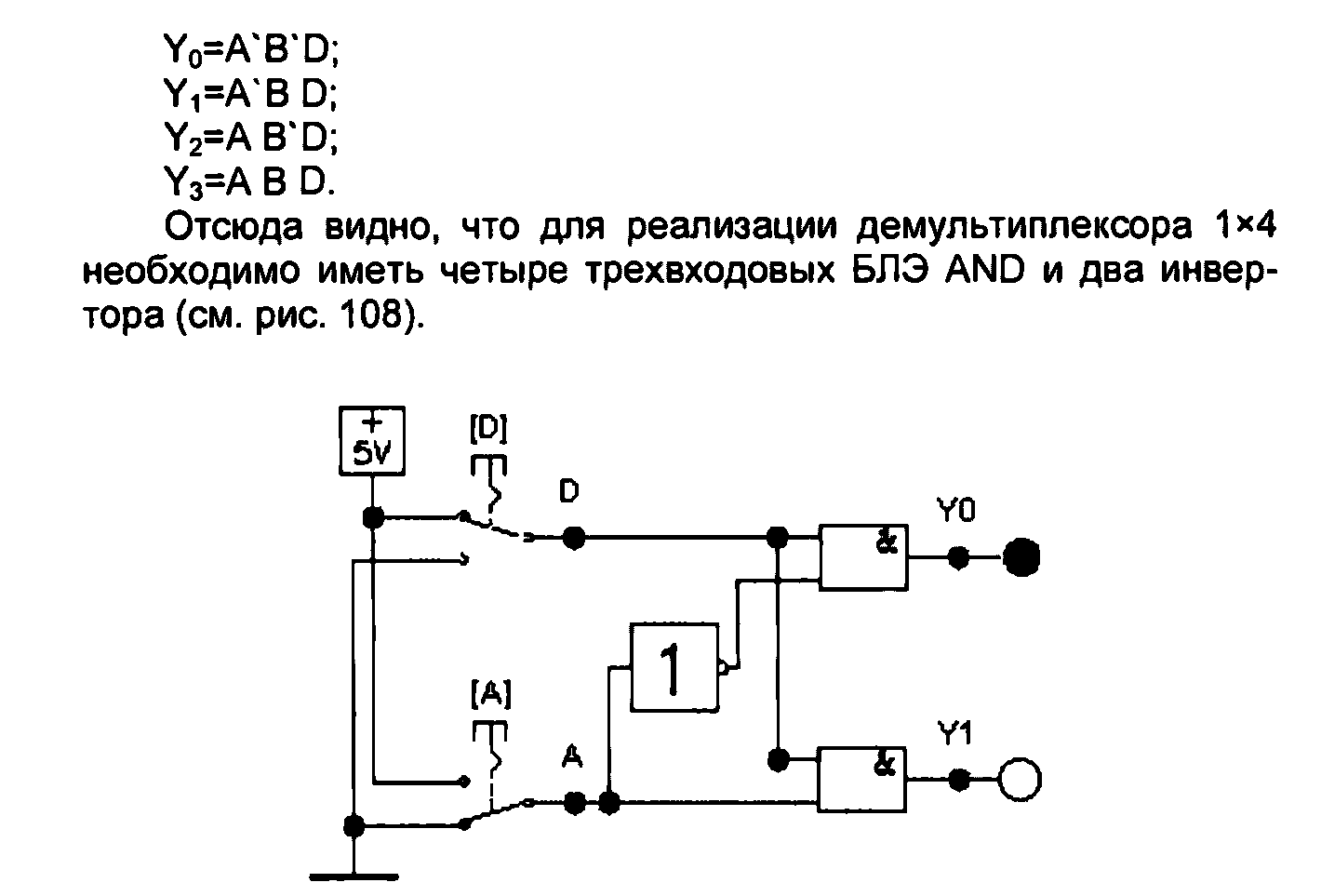

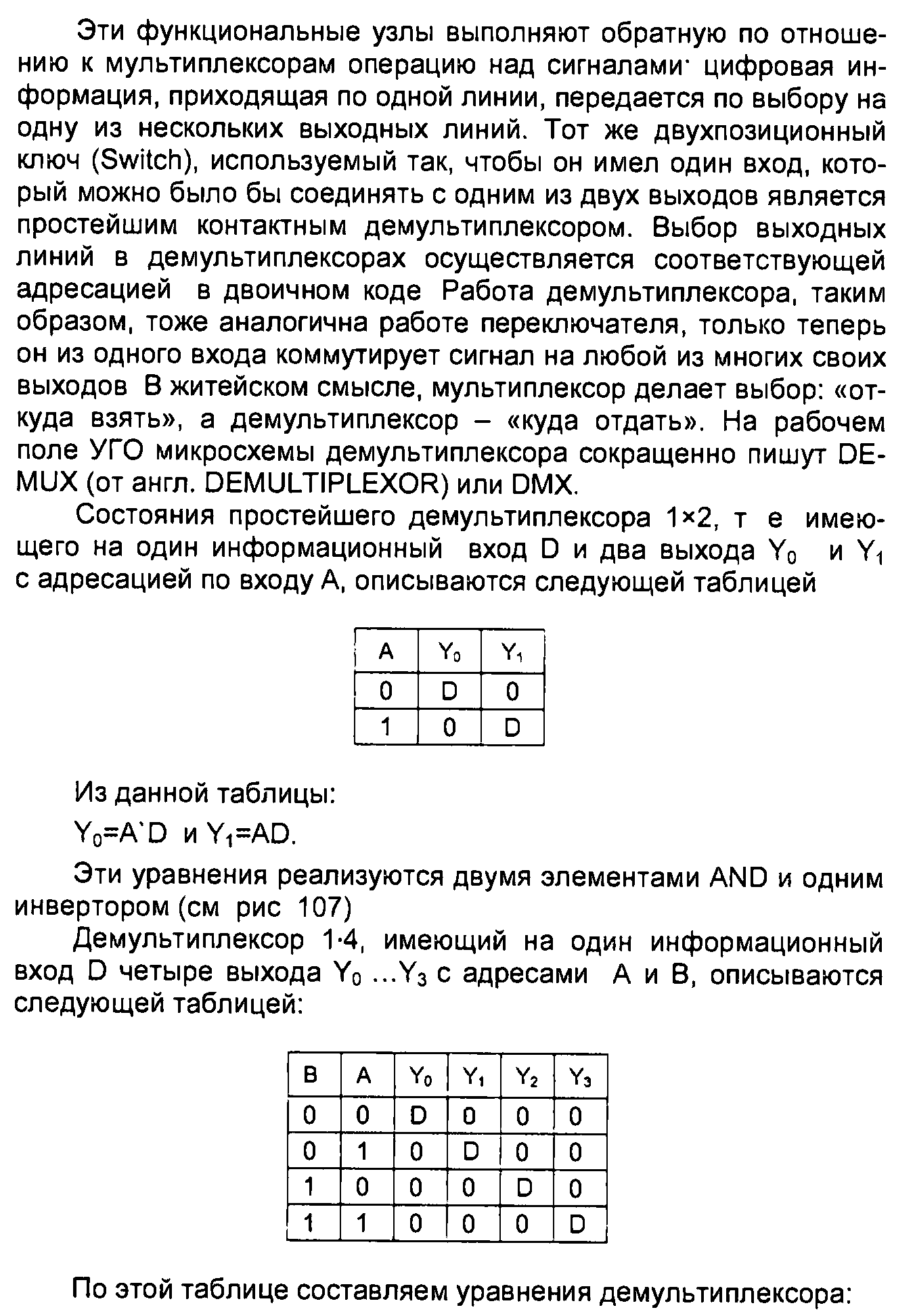

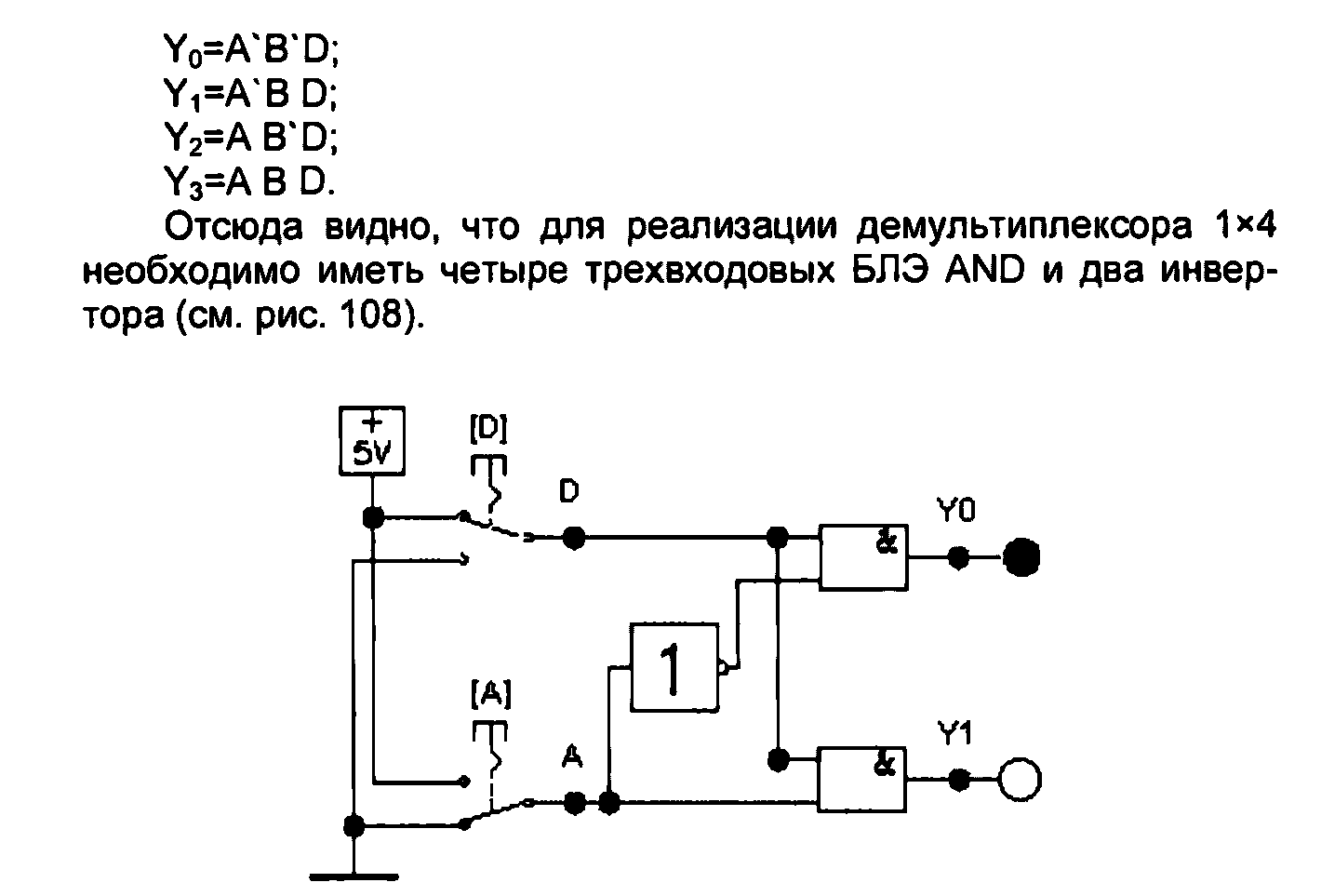

Теоретическая часть

Задание 1.

Собрать схему демультиплексора и проверить ее работу по таблице истинности

Задание 2.

Собрать схему демультиплексора на базе микросхемы и проверить ее работу по таблице истинности

Практическая работа №18

Тема: Исследование работы компаратора на ИМС.

Цель: Получить практические навыки исследования работы компараторов.

Изучение назначения устройства и принцип работы цифрового компаратора.

Цифровые компараторы (от английского compare – сравнивать) выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А=В или неравенства АB. Результат сравнения отображается в виде логического сигнала на одноименных выходах, в случае выполнения условия на выходе 1.

Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для выполнения условных переходах.

Задание 1.

-

Собрать схемы одноразрядных компараторов приведены и составить таблицу истинности. Операция A B)

Схема A

Схема A>B (A

B’)

B’)

Схема А=В (A’

B’+AB)

B’+AB)

Задание 2.

Построить схемы операций >=, <=, <> и проверить таблицы истинности.

Логические функции этих компараторов выглядят:

(A'·B)', (A·B')', (A'·B'+A·B)'.

Можем упростить данные формулы с помощью законов алгебры логики:

(A'·B)'=A''+B'=(закон де Моргана)=A+B' (закон двойного отрицания),

(A·B')'=A'+B''=A'+B,

(A'·B'+A·B)'=(A''+B'')·(A'+B')=(A+B)·(A'+B').

Практическая работа №19

Тема Исследование работы двоичного сумматора на ИМС.

Цель работы: изучение принципов построения и специфики применения комбинационных сумматоров в типовых арифметических узлах.

Задание 1. Исследование сумматоров:

1. Построить схему полусумматора и проверить таблицу истинности.

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода C

-

Построить схему полусумматора с подключением генератора слов и графического анализатора.

2.1. В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,2,3,4,5,6,7.

2

.2. Развернуть графический анализатор.

.2. Развернуть графический анализатор.2.3. Запустить генератор слов в пошаговом режиме, кнопка Step и проследить как будет меняться окно графического анализатора.

-

извлечь из магазина компонентов (раздел Comb’l) полусумматор и проверить его функционирование на соответствие таблице истинности.

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода С

4. Построить схему полного сумматора и проверить таблицу истинности.

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода С

5. извлечь из магазина компонентов полный одноразрядный сумматор и проверить его функционирование на соответствие таблице истинности

Схема, отражающая состояние выхода S

Схема, отражающая состояние выхода С

6. Собрать схему полусумматора на логических элементах И-ИЛИ-НЕ

6.1. В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,2,3,4,5,6,7.

6.2. Развернуть графический анализатор.

6.3. Запустить генератор слов в пошаговом режиме, кнопка Step и проследить как будет меняться окно графического анализатора.

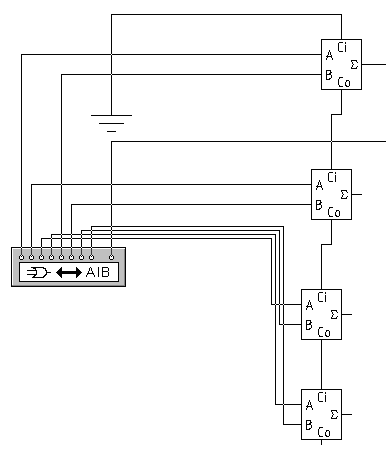

Задание 2

С

обрать на основе полных одноразрядных сумматоров 4-разрядный параллельный сумматор с последовательным переносом и проверить его работу, задавая на входы А и В и вход переноса различные двоичные числа. Для формирования двоичных чисел можно использовать в качестве логического 0 шину земли, а в качестве логической 1 источник напряжения 5В из раздела Passive магазина компонентов;

обрать на основе полных одноразрядных сумматоров 4-разрядный параллельный сумматор с последовательным переносом и проверить его работу, задавая на входы А и В и вход переноса различные двоичные числа. Для формирования двоичных чисел можно использовать в качестве логического 0 шину земли, а в качестве логической 1 источник напряжения 5В из раздела Passive магазина компонентов;Записать таблицу истинности для четырех выходов S и выхода переноса С

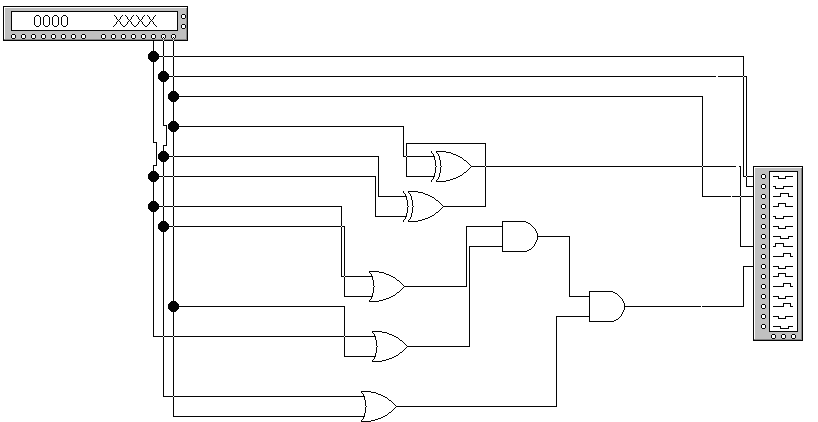

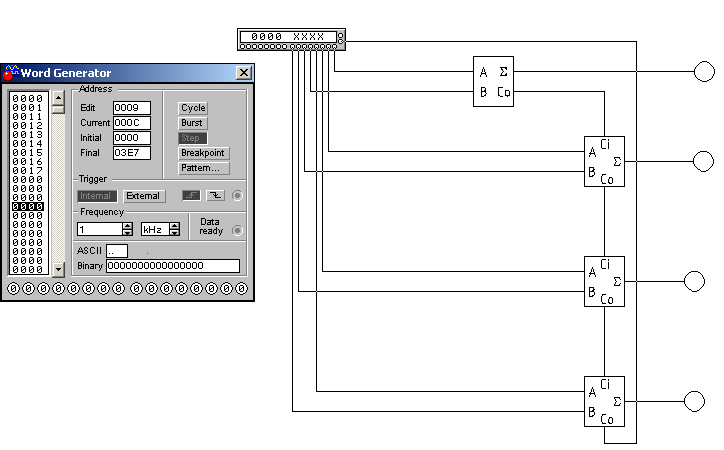

Исследовать четырехразрядный сумматор с помощью генератора слов.

-

Собрать схему согласно чертежа. -

Подключить 4 индикатора. -

В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,11,12,13,14,15,16,17. -

Запустить генератор в режиме Step.

10. Собрать цифровую схему сравнения.

10.1. В лицевой панели генератора ввести шестнадцатеричные цифры: 0,1,2,3,4,5,6,7.

10.2. Развернуть графический анализатор.

10 .3. Запустить генератор слов в пошаговом режиме, кнопка Step и проследить как будет меняться окно графического анализатора.

Задание 3.

Собрать схему на базе микросхемы и проверить ее работу.

Практическая работа №20

Тема: Исследование работы АЛУ на ИМС.

Цель работы

Изучение функциональных возможностей, области применения и приобретение навыков работы с арифметико-логическими устройствами (АЛУ) на примере микросхемы К155ИП3.

Задание 1.

Построить схему сложения двух чисел А и В.

С

оберем схему на основе микросхемы К155ИП3. В программе Electronics Workbench это микросхема из группы74181

оберем схему на основе микросхемы К155ИП3. В программе Electronics Workbench это микросхема из группы74181

Так как входы А0, А1, А2, А3 и В0, В1, В2, В3 инверсны, то перед ними ставим элементы НЕ. Входы М и СN заземляем, так кА работаем по отрицательной логике.

Откроем окно генератора слов.

A3 – A0 B3 – B0 S3 – S0

.

Для арифметического сложения, А плюс В на вход А подадим 7(0111) на вход В 2 (0010) на входы S 9(1001) согласно таблице. На выходе получим результат 9 и 0 в переносе.

Задание: Проверить все арифметические и логические операции таблицы работы АЛУ и отразить в своих примерах.

Пример проверить арифметическую операцию А плюс (

) при А=516, В=С16

) при А=516, В=С16 - Логическое сложение, плюс арифметическое сложение

- Логическое сложение, плюс арифметическое сложение| Логическое сложение  : : | Логическое умножение АВ: | Арифметическое сложение |

| 0+0=0 0+1=1 1+0=1 1+1=1 | 0*0=0 0*1=0 1*0=0 1*1=1 | 0+0=0 0+1=1 1+0=1 1+1=10 |

В окне генератора слов введем: 5С40 (числа А и В и код операции 4). Т. К. операция арифметическая, М=0 и L=0.

С16

+ 0101

+ 01010011

0111

А плюс (

)= + 0101

)= + 01010111

1100

Задание 2.

Проверить работу АЛУ в режиме компаратора. Для этого к выходу А=В (14) подключим индикатор.

По таблице (отрицательная логика) Проверим А>B. Выход CN=0. Подав на генератор слов комбинацию С560, проверим А=В (0), СN=1

З

адание: Проверить работe АЛУ в режиме компаратора и отразить в своих примерах.

адание: Проверить работe АЛУ в режиме компаратора и отразить в своих примерах.Практическая работа №21.

Тема: Синтез триггерной схемы

Цель: получить практические навыки создания и демонстрации работы триггерной схемы.

Задание

Спроектируйте синхронный триггер с информационными входами А и В, работающий в соответствии с заданной таблицей переключений, в двух вариантах: 1 - на основе JK-триггера; 2 - на основе D-триггера. В табл. 1 указаны состояния триггера до (Qn) и после (Qn+1) поступления синхросигнала.

| А | В | Qn | (Qn+1) по варианту | ||||||||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1. | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0. | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| А | В | Qn | (Qn+1) по варианту | ||||||||||||||

| 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | |||

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |